ISSN: 2302-9285, DOI: 10.11591/eei.v12i1.4357

# Performance analysis of CMOS based analog circuit design with PVR variation

Pankaj P. Prajapati, Anilkumar J. Kshatriya, Sureshbhai L. Bharvad, Abhay B. Upadhyay Department of Electronics and Communication Engineering, Lalbhai Dalpatbhai College of Engineering, Ahmedabad, India

#### **Article Info**

## Article history:

Received Jul 12, 2022 Revised Sep 17, 2022 Accepted Oct 4, 2022

#### Keywords:

CMOS CS CSPSO PSO PVT

#### **ABSTRACT**

Process, supply voltage, and temperature (PVT) are three important factors which contribute to performance variation of the complementary metal–oxide–semiconductor (CMOS) based analog circuits. In this paper, CMOS based analog circuit design with the PVT variation effects are explored. The effects of the PVT variation on the performance of CMOS based analog circuits are introduced. The optimization of CMOS based analog circuits such as differential amplifier (DA) and two-stage operational amplifier (op amp) circuits with PVT variations with different algorithms such as cockoo search (CS), particle swam optimization (PSO), hybrid CSPSO, and differential evaluation (DE) algorithms is presented. Each algorithm is implemented using the C programming language, interfaced with Ngspice circuit simulator, and tested on the Intel®core<sup>TM</sup> i5, 2.40 GHz processor with 8 GB internal RAM using the Ubuntu operating system (OS). The result shows PVT variation affects the performance of CMOS circuit.

This is an open access article under the CC BY-SA license.

141

## Corresponding Author:

Pankaj P. Prajapati

Department of Electronics and Communication Engineering, Lalbhai Dalpatbhai College of Engineering Ahmedabad, Guiarat, India

Email: pankaj@ldce.ac.in

# 1. INTRODUCTION

The three important factors which contribute to performance variation of the complementary metal–oxide–semiconductor (CMOS) based analog circuits are process, voltage, and temperature (PVT) variations. The deviation in a fabrication creates process variations. The parameters which can create process variations can be impurity concentration densities, oxide thicknesses, and diffusion depths. This introduces variations in the sheet resistance and transistor parameters such as threshold voltage. This causes variations in (W/L) of MOS transistors. There are generally five possible process corners. They are known as typical-typical (TT), fast-fast (FF), slow-slow (SS), fast-slow (FS), and slow-fast (SF). The second parameter is the power supply on which MOS transistor performance depends. The variation in the supply voltage affects the saturation current which inflects the propagation delay of a cell. The supply voltage is not constant throughout the chip, hence the prorogation delay varies in a chip. Third factor is temperature variation that is unavoidable in the everyday operation of a design. The temperature can vary throghout the chip during chip operation. This happens due to the power dissipation in the MOS transistors. The power consumption is generally due to switching, short-circuit and leakage power consumption.

# 2. CIRCUIT DESIGN WITH PVT CORNERS

Cockoo search (CS) [1], [2], particle swam optimization (PSO) [3]–[5], differential evaluation (DE) [6], [7], and hybrid CSPSO [8] algorithms are tested for optimization of CMOS based analog circuits with

Journal homepage: http://beei.org

142 □ ISSN: 2302-9285

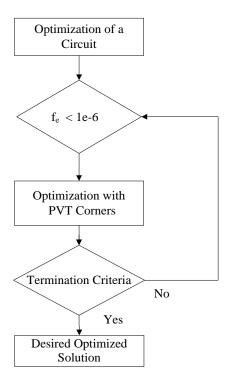

fixed PVT in different literature [9], [10]. By individually varying PVT factors over their permissible ranges, PVT variations can be taken into account. Analyzing subsequent combinations of above parameters are called PVT corners. In modern designs, there can be hundreds or thousands of PVT corners are posssible. The major intend of PVT analysis is to find the worst-case performance values across user-defined PVT corners. The strength and yield of the designed circuit are increased by guaranteeing that it complies with all design goals and constraints in some/all corners. The problem is that simulating each corner can take several seconds or minutes based on the complexity of the circuit. To simulate all possible corners could take hours or even days. Here, we have considered three process corners i.e TT, FF, and SS, three values of a supply voltage, and three values of temperature during PVT aware circuit design as a proof of concept. So, there would be a total of  $3\times3\times3=27$  combinations of the PVT corners. Two-step approach, as shown in Figure 1, is used to find the worst case performance with PVT analysis [8]–[11]. Different algorithm is discussed in defferent literatures [12]–[23].

Figure 1. Two-step approach for circuit design with PVT variations [8], [11]

PVT corners are used within iterative circuit optimization loop for PVT-aware circuit optimization. After circuit optimization with the required fitness function value by the optimizer which is implemented using an evolutionary algorithms (EA), the circuit is tested with user-defined PVT corners. If the circuit gives required fitness value for each user-defined PVT corners then the optimization process will stop. If the circuit does not give required fitness value for any user-defined PVT corners then the optimizer will redesign the circuit until the termination criteria are not fulfilled. The termination criteria are the maximum number of iterations that have been reached or minimum fitness function value is satisfied. This process will stop when the termination criteria will meet.

# 3. OPTIMIZATION OF ANALOG CIRCUITS

The PVT analysis is carried out for differential amplifier (DA) and two-stage operational amplifier (op-amp) circuits using  $0.18~\mu m$  CMOS technology during the optimization process with the CS, hybrid CSPSO, PSO, and DE algorithms.

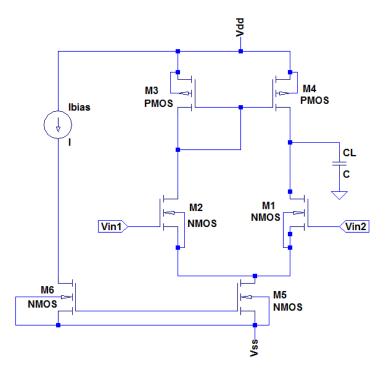

# 3.1. Optimization of DA

The circuit diagram of DA is shown in Figure 2 [24], [25]. We have set a length of M1 to M4 transistors of DA circuit as  $L_1=L_2=L_3=L_4=3.5 \mu m$ , a length of  $M_5$  and  $M_6$  transistors as  $L_5=L_6=1.4 \mu m$ . The

circuit is optimized to drive the load capacitor of 0.5 pF. The supply voltage is set to  $\pm 1.8$  V. Design parameters and search space of design parameters for DA using 0.18  $\mu$ m CMOS technology are listed in Table 1. Desired specifications for this circuit using 0.18  $\mu$ m CMOS technology are listed in Table 2.

ISSN: 2302-9285

Figure 2. DA using a current mirror load [25]

Table 1. Design parameter and search space for DA using 0.18 µm CMOS technology

| Sr. No. | Design parameters | Search space of design parameters |

|---------|-------------------|-----------------------------------|

| 1       | $W_1=W_2 (\mu m)$ | 3.5 µm to 30 µm                   |

| 2       | $W_3=W_4 (\mu m)$ | 3.5 µm to 30 µm                   |

| 3       | $W_5=W_6 (\mu m)$ | 3.5 µm to 30 µm                   |

| 4       | $I_{bias}(\mu A)$ | 3.5 μA to 30 μA                   |

Table 2. Desired specifications for DA using 0.18 µm CMOS technology

| Sr. No. | Specifications         | Desired value |

|---------|------------------------|---------------|

| 1       | $A_V(dB)$              | >39           |

| 2       | UGB (MHz)              | > 10          |

| 3       | PM (°)                 | > 45          |

| 4       | +ve PSSR (dB)          | >35           |

| 5       | - ve PSSR (dB)         | >60           |

| 6       | RSR (V/µs)             | >9            |

| 7       | FSR (V/µs)             | >9            |

| 8       | CMRR (dB)              | >50           |

| 9       | P <sub>diss</sub> (mw) | < 1           |

| 10      | $N_{in} (nV^2/Hz)$     | < 1e-6        |

| 11      | $N_{op} (nV^2/Hz)$     | < 1e-4        |

| 12      | TTA (µm <sup>2</sup> ) | < 1500        |

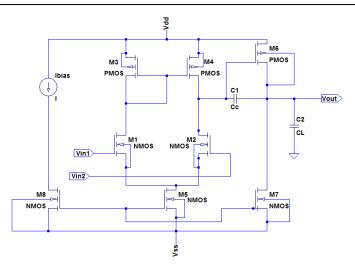

# 3.2. Optimization of two-stage OP-AMP

We have also optimized two-stage op-amp circuit using 0.18  $\mu$ m CMOS technology at different PVT corners by the CS, hybrid CSPSO, PSO, and DE algorithms. The circuit diagram of the two-stage op-amp is given in the Figure 3 [24], [25]. We have set a length of  $M_1$ ,  $M_2$ ,  $M_5$ ,  $M_7$ , and  $M_8$  transistors as  $L_1=L_2=L_5=L_7=L_8=0.75$   $\mu$ m and a length of  $M_3$ ,  $M_4$ , and  $M_6$  transistors as  $L_3=L_4=L_6=0.50$   $\mu$ m for the optimization process with PVT corners using 0.18  $\mu$ m CMOS technology. Design parameters and search space of design parameters for this circuit using 0.18  $\mu$ m CMOS technology are listed in Table 3. Desired specifications for this circuit using 0.18  $\mu$ m CMOS technology with are listed in Table 4.

144 □ ISSN: 2302-9285

Figure 3. Two-stage op-amp [12], [13]

Table 3. Design parameters and search space for op-amp using 0.18 µm CMOS technology

| Sr. No. | Design parameters      | Search space of design parameters |

|---------|------------------------|-----------------------------------|

| 1       | $W_1=W_2 (\mu m)$      | 1 μm to 10 μm                     |

| 2       | $W_3=W_4(\mu m)$       | 1 μm to 10 μm                     |

| 3       | $W_5=W_8 (\mu m)$      | 1 μm to 10 μm                     |

| 4       | $W_6(\mu m)$           | 1 μm to 10 μm                     |

| 5       | $W_7(\mu m)$           | 1 μm to 10 μm                     |

| 6       | I <sub>bias</sub> (μA) | 1 μA to 10 μA                     |

Table 4. Desired specifications for op-amp using 0.18 µm CMOS technology

| - | -       |                        |               |

|---|---------|------------------------|---------------|

|   | Sr. No. | Specifications         | Desired value |

|   | 1       | $A_{V}(dB)$            | > 60          |

|   | 2       | UGB (MHz)              | > 10          |

|   | 3       | PM (°)                 | > 45          |

|   | 4       | +ve PSSR (dB)          | > 70          |

|   | 5       | - ve PSSR (dB)         | > 70          |

|   | 6       | RSR (V/µs)             | > 10          |

|   | 7       | FSR (V/µs)             | > 10          |

|   | 8       | CMRR (dB)              | > 60          |

|   | 9       | P <sub>diss</sub> (mw) | < 1           |

|   | 10      | $N_{in}(nV^2/Hz)$      | < 1e-6        |

|   | 11      | $N_{op}(nV^2/Hz)$      | < 1e-4        |

|   | 12      | $TTA (\mu m^2)$        | < 300         |

## 4. RESULTS AND DISCUSSION

Design parameters optimized by different EAs for DA using 0.18  $\mu m$  CMOS technology at different PVT corners are listed in Table 5. Obtained specifications by different EAs for this circuit using 0.18  $\mu m$  CMOS technology at different PVT corners are listed in Table 6. The CS and CSPSO algorithms optimized this circuit for the desired specifications with transport-triggered architecture (TTA) of 206.36  $\mu m^2$  and 195.85  $\mu m^2$  respectively. The TTA obtained by the CS and CSPSO algorithms is less as compared to that achieved by the DE and PSO algorithms. The performance of the CS, hybrid CSPSO, PSO, and DE algorithms for optimization of this circuit using 0.18  $\mu m$  CMOS technology with PVT variations for 10 independent runs is listed in Table 7.

Table 5. Design parameters optimized by different EAs for DA using 0.18 μm CMOS technology at different PVT corners

| 1 VI Corners |                          |       |       |       |       |  |

|--------------|--------------------------|-------|-------|-------|-------|--|

| Sr. No.      | Design parameters        | PSO   | DE    | CS    | CSPSO |  |

| 1            | $W_1=W_2 (\mu m)$        | 24.10 | 28.63 | 17.75 | 17.22 |  |

| 2            | $W_3=W_4 (\mu m)$        | 20.19 | 13.88 | 9.03  | 3.50  |  |

| 3            | $W_5=W_6 (\mu m)$        | 26.03 | 23.77 | 24.79 | 18.14 |  |

| 4            | $I_{\text{bias}}(\mu A)$ | 5.29  | 14.72 | 10.00 | 10.00 |  |

|              |                          |       |       |       |       |  |

П

Table 6. Obtained specifications by different EAs for DA using 0.18 µm CMOS technology at different PVT corners

| Sr. No. | Specifications         | PSO      | DE       | CS       | CSPSO    |

|---------|------------------------|----------|----------|----------|----------|

| 1       | $A_V(dB)$              | 38.97    | 39.04    | 39.36    | 39.35    |

| 2       | UGB (MHz)              | 14.00    | 25.68    | 25.17    | 21.70    |

| 3       | PM (°)                 | 49.83    | 45.44    | 51.60    | 53.50    |

| 4       | +ve PSSR (dB)          | 40.48    | 40.99    | 40.86    | 41.36    |

| 5       | - ve PSSR (dB)         | 72.52    | 72.54    | 71.59    | 68.51    |

| 6       | RSR (V/µs)             | 14.68    | 33.47    | 27.16    | 23.66    |

| 7       | FSR (V/µs)             | 9.96     | 23.12    | 19.55    | 18.62    |

| 8       | CMRR (dB)              | 58.33    | 55.67    | 58.60    | 56.10    |

| 9       | P <sub>diss</sub> (mw) | 0.03     | 0.07     | 0.05     | 0.05     |

| 10      | $N_{in} (nV^2/Hz)$     | 2.66e-07 | 1.51e-07 | 1.27e-07 | 1.53e-07 |

| 11      | $N_{op} (nV^2/Hz)$     | 1.91e-06 | 2.17e-06 | 1.64e-06 | 1.82e-06 |

| 12      | TTA (μm <sup>2</sup> ) | 382.95   | 364.08   | 256.86   | 195.85   |

Table 7. Performance of different EAs for optimization of DA using 0.18 µm CMOS technology with PVT variations

| Algorithm | $SD_{fitness}$ | $I_{avg}$ | $FE_{avg}$ | $S_{rate}$ | $T_{sim}(s)$ |

|-----------|----------------|-----------|------------|------------|--------------|

| DE        | 0.001403       | 36.10     | 1113       | 9          | 2511         |

| PSO       | 0.002032       | 60.4      | 1812       | 4          | 4428         |

| CS        | 0.004117       | 17.4      | 1074       | 9          | 2488         |

| CSPSO     | 0.0            | 30.9      | 2811       | 10         | 5594         |

The CSPSO algorithm succeeded 10 times, the CS and DE algorithms succeeded 9 times, and the PSO algorithm succeeded only 1 time out of 10 runs to achieve all specifications. The CS algorithm required less average iterations for 10 independent runs of the optimization process compared to those required for DE and PSO algorithms. The CSPSO algorithm also achieved zero standard deviation of fitness value. Thus, the performance of the CS and CSPSO algorithms outperform compared to DE and PSO algorithms for this case.

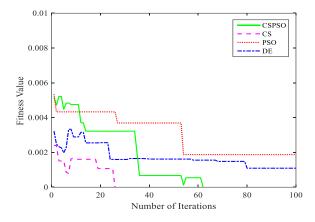

The convergence graph of CS, CSPSO, DE, and PSO algorithms for the optimization of DA using 0.18  $\mu m$  CMOS technology at different PVT corners is shown in Figure 4 which shows that the CS algorithm is faster to reach at target fitness value as compared to DE, CSPSO, and PSO algorithms. Design parameters optimized by different EAs for this circuit using 0.18  $\mu m$  CMOS technology with PVT variations are listed in Table 8. Obtained specifications by different EAs for this circuit using 0.18  $\mu m$  CMOS technology with PVT variations are listed in Table 9.

Figure 4. Convergence graph of different EAs for DA optimization using  $0.18~\mu m$  CMOS technology at different PVT corners

Table 8. Design parameters optimized by different EAs for Op-amp using 0.18 µm CMOS technology at different PVT corners

|         | GIIIC                    | 101101 1 1 | COINCID |      |       |

|---------|--------------------------|------------|---------|------|-------|

| Sr. No. | Design parameters        | PSO        | DE      | CS   | CSPSO |

| 1       | $W_1=W_2(\mu m)$         | 9.50       | 10.00   | 1.70 | 1.52  |

| 2       | $W_3=W_4 (\mu m)$        | 7.12       | 6.81    | 3.32 | 3.90  |

| 3       | $W_5=W_8 (\mu m)$        | 9.02       | 10.00   | 3.55 | 5.38  |

| 4       | $W_6(\mu m)$             | 9.78       | 9.67    | 8.53 | 10.00 |

| 5       | $W_7(\mu m)$             | 10.00      | 10.00   | 5.85 | 7.15  |

| 6       | $I_{\text{bias}}(\mu A)$ | 9.04       | 10.00   | 9.95 | 9.13  |

146 ☐ ISSN: 2302-9285

Table 9. Obtained specifications by different EAs for Op-amp using 0.18  $\mu m$  CMOS technology at different

| F V I COILLEIS |                        |          |           |          |           |  |

|----------------|------------------------|----------|-----------|----------|-----------|--|

| Sr. No.        | Specifications         | PSO      | DE        | CS       | CSPSO     |  |

| 1              | $A_V(dB)$              | 66.42    | 66.54     | 68.38    | 68.84     |  |

| 2              | UGB (MHz)              | 25.55    | 21.51     | 11.81    | 10.83     |  |

| 3              | PM (°)                 | 27.90    | 106.20    | 45.19    | 48.71     |  |

| 4              | +ve PSSR (dB)          | 81.66    | 80.94     | 80.65    | 81.46     |  |

| 5              | - ve PSSR (dB)         | 90.06    | 91.62     | 90.75    | 109.84    |  |

| 6              | RSR (V/µs)             | 15.69    | 15.07     | 15.42    | 15.11     |  |

| 7              | FSR (V/µs)             | 10.89    | 9.95      | 13.70    | 12.25     |  |

| 8              | CMRR (dB)              | 73.94    | 73.11     | 72.97    | 71.69     |  |

| 9              | P <sub>diss</sub> (mw) | 0.07     | 0.07      | 0.11     | 0.10      |  |

| 10             | $N_{in} (nV^2/Hz)$     | 8.54e-08 | 1.37 e-07 | 3.51e-07 | 4.02 e-07 |  |

| 11             | $N_{op} (nV^2/Hz)$     | 2.40e-05 | 3.02 e-05 | 4.14e-05 | 4.65e-05  |  |

| 12             | TTA (μm <sup>2</sup> ) | 47.29    | 46.43     | 19.85    | 24.61     |  |

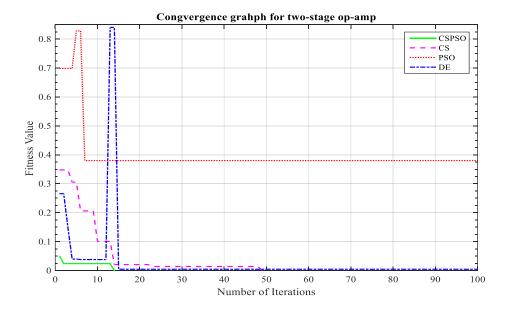

The CS algorithm optimized this circuit with least TTA of  $19.85~\mu m^2$  as compared to that achieved by other algorithms. The performance of the CS, PSO, hybrid CSPSO, and DE algorithms for optimization of this circuitusing  $0.18~\mu m$  CMOS technology for 10 independent runs is listed in Table 10. The CSPSO algorithm succeeded 6 times, the CS succeeded 3 times, and the DE algorithm succeeded only 1 time out of 10 runs to achieve all specifications, whereas the PSO algorithm did not succeed to achieve all specifications. The CSPSO and CS algorithms required less average iterations for 10 independent runs of the optimization process of this circuit compared to those required for DE and PSO algorithms. Thus, the performance of the CSPSO and CS algorithms outperforms compared to both DE and PSO algorithms for this case also. The convergence graph of CS, CSPSO, DE, and PSO algorithms for the optimization of two-stage op-amp using  $0.18~\mu m$  CMOS technology is shown in Figure 5 which shows that the CSPSO algorithm is faster to reach at target fitness value as compared to DE, CS, and PSO algorithms.

Table 10. Performance of different EAs for optimization of op-amp using 0.18 µm CMOS technology with

| PVT variations |                |           |            |            |              |  |  |

|----------------|----------------|-----------|------------|------------|--------------|--|--|

| Algorithm      | $SD_{fintess}$ | $I_{avg}$ | $FE_{avg}$ | $S_{rate}$ | $T_{sim}(s)$ |  |  |

| DE             | 0.378508       | 90.4      | 3,030      | 1          | 4879         |  |  |

| PSO            | 0.269239       | 100       | 3,000      | 0          | 4765         |  |  |

| CS             | 0.106352       | 85.30     | 5,148      | 3          | 8140         |  |  |

| CSPSO          | 0.282675       | 66        | 5,970      | 6          | 9651         |  |  |

Figure 5. Convergence graph of different EAs for two-stage op-amp optimization using 0.18  $\mu m$  CMOS technology

#### **CONCLUSION**

In this paper, the focus is set on PVT-aware circuit optimization to find a design which meets desired specifications across all user-defined PVT corners. DA and two-stage op-amp circuits with different 27 PVT corners are optimized for required specifications using 0.18 µm CMOS technology by different metaheuristic EAs. The performance of each EA is also compared for PVT-aware design of DA and twostage op-amp circuits. The CS and CSPSO algorithms outperform compared to both DE and PSO algorithms for PVT-aware circuit optimization. The PVT analysis is important to develop a robust optimizer.

#### REFERENCES

- X. -S. Yang and S. Deb, "Cuckoo Search via Lévy flights," in 2009 World Congress on Nature & Biologically Inspired Computing (NaBIC), 2009, pp. 210–214, doi: 10.1109/NABIC.2009.5393690.

E. Valian, S. Mohanna, and S. Tavakoli, "Improved Cuckoo search algorithm for global optimization," *International Journal of*

- Communication Information Technology, vol. 1, no. 1, pp. 31–44, 2011.

- J. Kennedy and R. Eberhart, "Particle swarm optimization," in Proceedings of ICNN'95-International Conference on Neural Networks, 1995, vol. 4, pp. 1942-1948, doi: 10.1109/ICNN.1995.488968.

- J. Kennedy and R. C. Eberhart, Swarm intelligence. San Francisco: Morgan Kaufmann Publishers, 2001.

- Y. Shi and R. C. Eberhart, "Empirical study of particle swarm optimization," in *Proceedings of the 1999 Congress on Evolutionary Computation-CEC99 (Cat. No. 99TH8406)*, 1999, pp. 1945–1950, doi: 10.1109/CEC.1999.785511.

- S. Rainer and P. Kenneth, "Differential evolution: a simple and efficient heuristic for global optimization over continuous spaces," Journal of Global Optimization, vol. 11, no. 4, pp. 341-359, 1997.

- V. Arunachalam, "Water resources research report: optimization using differential evolution," Canada, 2008.

- P. P. Prajapati, "Computer aided CMOS based analog circuit design," Ph.D. dissertation, Department Electronics & [8] Communication Engineering, Lalbhai Dalpatbhai College of Engineering, Ahmedabad, India, 2019.

- P. Sarkar, N. M. Laskar, S. Nath, K. L. Baishnab, and S. Chanda, "Offset voltage minimization based circuit sizing of CMOS operational amplifier using whale optimization algorithm," Journal of Information and Optimization Sciences, vol. 39, no. 1, pp. 83–98, Jan. 2018, doi: 10.1080/02522667.2017.1372913.

- [10] M. A. M. Majeed and S. R. Patri, "A hybrid of WOA and mGWO algorithms for global optimization and analog circuit design automation," COMPEL-The international journal for computation and mathematics in electrical and electronic engineering, vol. 38, no. 1, pp. 452-476, Jan. 2019, doi: 10.1108/COMPEL-04-2018-0175.

- [11] J. Ramos, ASCO: a SPICE circuit optimizer. Boston, MA: Free Software Foundation, 2016.

- B. Razavi, Design of analog CMOS integrated circuits. United States: Mc Graw Hill Education, 2015.

- [13] G. Alpaydin, S. Balkir, and G. Dundar, "An evolutionary approach to automatic synthesis of high-performance analog integrated circuits," IEEE Transactions on Evolutionary Computation, vol. 7, no. 3, pp. 240-252, Jun. 2003, doi: 10.1109/TEVC.2003.808914.

- [14] S. S. Sapatnekar, V. B. Rao, P. M. Vaidya, and S.- M. Kang, "An exact solution to the transistor sizing problem for CMOS circuits using convex optimization," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 12, no. 11, pp. 1621–1634, 1993, doi: 10.1109/43.248073.

- M. M. Hershenson, S. P. Boyd, and T. H. Lee, "Optimal design of a CMOS op-amp via geometric programming," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 20, no. 1, pp. 1–21, 2001, doi: 10.1109/43.905671.

- [16] P. P. Prajapati and M. V. Shah, "Optimization of CMOS current mirror load-based differential amplifier using hybrid Cuckoo Search and particle swarm optimization algorithm," Journal of Artificial Intelligence Research & Advances, vol. 5, no. 3, pp. 71-78, 2018.

- [17] P. P. Prajapati and M. V. Shah, "Two stage CMOS operational amplifier design using particle swarm optimization algorithm," in 2015 IEEE UP Section Conference on Electrical Computer and Electronics (UPCON), Dec. 2015, pp. 1-5, doi: 10.1109/UPCON.2015.7456700.

- P. P. Prajapati and M. V. Shah, "Automatic sizing of CMOS-based analogue circuits using Cuckoo search algorithm," International Journal of Intelligent Systems Technologies and Applications, vol. 19, no. 2, pp. 125-140, 2020, doi: 10.1504/IJISTA.2020.107217.

- R. A. Thakker, C. Sathe, A. B. Sachid, M. S. Baghini, V. R. Rao, and M. B. Patil, "A novel table-based approach for design of FinFET circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 28, no. 7, pp. 1061-1070, Jul. 2009, doi: 10.1109/TCAD.2009.2017431.

- Y. Massoud, A. Nieuwoudt, and T. Ragheb, "Automated design solutions for fully integrated narrow-band low noise amplifiers," in 2006 6th International Workshop on System on Chip for Real Time Applications, Dec. 2006, pp. 109-114, doi: 10.1109/IWSOC.2006.348275.

- H. Y. Koh, C. H. Sequin, and P. R. Gray, "OPASYN: a compiler for CMOS operational amplifiers," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 9, no. 2, pp. 113-125, 1990, doi: 10.1109/43.46777.

- A. Savio, L. Colalongo, M. Quarantelli, and Z. M. K.- Vajna, "Automatic scaling procedures for analog design reuse," IEEE Transactions on Circuits and Systems 1: Regular Papers, vol. 53, no. 12, pp. 2539-2547, Dec. 2006, doi: 10.1109/TCSI.2006.883849.

- W. Nye, D. C. Riley, A. S.- Vincentelli, and A. L. Tits, "DELIGHT.SPICE: an optimization-based system for the design of integrated circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 7, no. 4, pp. 501-519, Apr. 1988, doi: 10.1109/43.3185.

- R. J. Baker, CMOS: Circuit Design, Layout, and Simulation. US: IEEE Press Series on Microelectronic Systems, 2012.

- P. E. Allen and D. R. Holberg, CMOS analog circuit design. England: Oxford University Press, 2002.

148 □ ISSN: 2302-9285

## **BIOGRAPHIES OF AUTHORS**

**Dr. Anilkumar J. Kshatriya** is currently working as an assistant professor in the Department of Electronics and Communication at Lalbhai Dalpatbhai College of Engineering, Gujarat, India. He has completely his Ph.D from GTU, Ahmedabad in 2016. He has more than 18 years of teaching experience. He has published many of papers in reputed journals and national and international conferences. He can be contacted at email: anil@ldce.ac.in.

Sureshbhai L. Bharvad had completed B.E. in Electronics and Communication Engineering from Ahmedabad Institute of Technology, Ognaj Ahmedabad in 2009. He completed M.E in 2013 from Vishvakarma Government Engineering College, Chandkheda in Signal Processing and VLSI Technology (EC). He currently persuing Ph.D from GTU, India. He working as assistant professor in LDCE since last 12 years. He can be contacted at email: slbharvad@gmail.com.

Abhay B. Upadhyay (a) S (a) is currently working as a assistant professor in Department of Electronics and Communication at Lalbhai Dalpatbhai College of Engineering, India. He completed M.E in 2008 from Charotar Institute of Technology, Changa in Electronics and Communication System Engineering (CSE). He working as assistant professor in LDCE since last 12 years. He can be contacted at email: abupadhyay1979@gmail.com.