ISSN: 2302-9285, DOI: 10.11591/eei.v12i2.4138

# A cascade multi-level inverter topology with reduced switches and higher efficiency

#### Osama Yaseen Khudair Al-Atbee, Khalid M. Abdulhassan

Department of Electrical Engineering, University of Basrah, Basrah, Iraq

#### **Article Info**

#### Article history:

Received May 27, 2022 Revised Aug 13, 2022 Accepted Sep 30, 2022

#### Keywords:

Inverter Multilevel inverters Sinusoidal pulse width modulation THD reduction

#### **ABSTRACT**

The use of multi-level inverter (MLI) technologies in high-power, mediumvoltage energy regulation has been more popular in recent years. Despite the fact that the multilayer inverter has a lot of benefits, it has certain disadvantages in the layer of higher levels due to the enormous number of semiconductor switches that it employs in its construction. This may result in the inverter being of a huge size and costing a lot of money, as well as a significant rise in losses. As a result, the new MLI is suggested to minimize the number of switches in order to alleviate these challenges. This article describes a cascaded multilevel inverter with lower devices. The suggested cascaded multilevel inverter is intended for use in minimizing total harmonic distortion (THD), as shown in MATLAB/Simulink by the graph. Multilevel inverters benefit from the switching pattern of semiconductor switches, which may be used to improve their overall performance. This approach lowers the switching loss while simultaneously increasing the efficiency. In order to validate the suggested approach, simulations are carried out using the MATLAB/Simulink programming environment.

This is an open access article under the CC BY-SA license.

668

# **Corresponding Author:**

Osama Yaseen Khudair Al-Atbee Department of Electrical Engineering, University of Basrah Basrah, Iraq

Email: usama.khader@uobasrah.edu.iq

#### 1. INTRODUCTION

In recent years, there has been a lot of interest in multi-level inverters (MLIs) because of their potential uses in industrial and electrical systems, as well as their minimal electromagnetic interference, ease of control, and high efficiency. Additionally, it is possible to link it up to various renewable energy sources such as wind turbines, and photovoltaic solar panels [1]-[8]. Since 1970, various topologies have been developed [9]. The two-level inverter is the most common type of inverter, and it is named for the fact that it produces two different voltage levels. However, the performance of this inverter is affected by a high level of total harmonic distortion (THD), leading to the need of a large filter size, a high voltage rating for the switches, a high switching frequency, which results in additional switching losses, increased voltage stress on the switches, and electromagnetic interference. The two-level inverter can only be utilized for applications that involve low and medium voltage [10]-[15]. This is because the switches have a high voltage rating and are subject to voltage stress. This brings up the requirement for a different configuration. MLI is presented in order to provide a DC/AC conversion that has significantly improved performance and significantly reduced THD [16]-[18].

The best operation of most electrical applications is ensured by using a sinusoidal waveform supply [19]-[21]. With an increase in the number of inverter levels, the output voltage becomes more similar to a sinusoidal waveform, hence lowering the THD [22], [23]. When compared to the hard-switched two-level

Journal homepage: http://beei.org

pulse width modulation (PWM) inverter, the MLI has a number of advantages, including a lower dv/dt at high power operation and higher efficiency [24]-[26].

Generally, there are three main topologies for MLIs: cascade, diode clamp, and capacitor clamp. Among these topologies are the following: the cascade MLI is the simplest to construct and has the fewest number of components [24], [27]. Typically, cascade MLI is made up of a number of switches and DC sources that are all connected in series. To generate alternating current voltage with several levels, the switches must be toggled on and off in order to achieve the fundamental voltage and eliminate the higher order harmonics in the output. In this paper, a cascade of MLIs is presented and compared with three inverter topologies to get the fewest number of switches possible to reduce the size and cost of the converter and to reduce switching losses by reducing the number of switches in the on-state during each mode of operation, which improves efficiency.

#### 2. RESEARCH METHOD

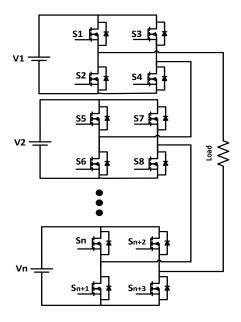

# 2.1. Conventional cascade bridge MLI topology

Figure 1 depicts the conventional cascade bridge MLI topology that is commonly used [22]. The output voltage level of this inverter is:

$$k = (N+2)/2 \tag{1}$$

where N represents the number of switches necessary to achieve the desired voltage level.

Figure 1. The conventional cascade bridge MLI

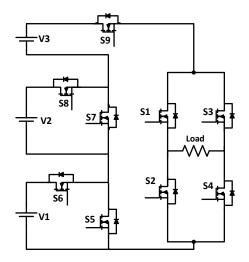

# 2.2. The cascade MLI topologies

The topology for the cascade MLI as a modified topology for the cascade bridge MLI as shown in Figure 2 [28]. As can be seen in Figure 2, the number of switches in the level marker part is 5, with three individual DC sources to form two cascade cells connected in series, in addition to the four switches in the H-bridge part. The number of output voltage levels depends upon the number of cells. The number of switches is reduced considerably compared to the conventional cascade bridge MLI for the same output voltage level. To reduce the THD in the output voltage the number of output voltage levels must be increased but this will require more DC sources and switches and need more complex control circuit. The output voltage level of this inverter is:

$$k = N - 2 \tag{2}$$

$$N = 2n + 3 \tag{3}$$

Where N is number of switches and n is the number of DC sources.

670 ISSN: 2302-9285

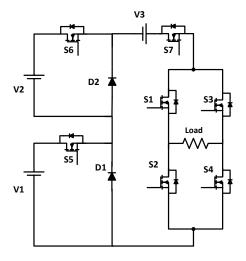

The 7-level cascade MLI topology in [7] can be improved as shown in Figure 3. In this figure, one of the two switches in each cell is replaced by a diode. The required number of switches and diodes required can be calculated as:

Number of switches

$$(N) = n + 4$$

(4)

The number of diodes =

$$(k-3)/2$$

(5)

Figure 2. The cascade bridge 7-level inverter

Figure 3. The modified 7-level MLI circuit in [7]

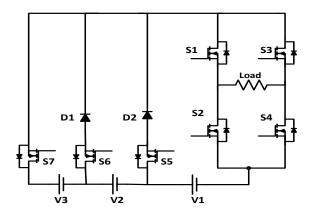

Gajula [29] shows an amazing topology for cascade MLIs as shown in Figure 4. In this topology the maximum output voltage, the number of individual DC sources, the number of switches and the number of diodes is as in above circuit but in this topology only one switch is at on state in each level of output voltage with a reduced number of diodes in each level that are inversely proportional with number of levels that lead to reduce the losses of the switches and increase the efficiency.

Figure 4. The modified 7-level MLI circuit in [29]

#### 3. THE TOPOLOGY OF THE PROPOSED CIRCUIT

The proposed cascade MLI circuit is shown in Figure 5. In this topology, the maximum output voltage, the number of individual DC sources, the number of switches, and the number of diodes are as in section c. The main difference in this circuit is that only one diode will work at each level, which is the main difference from the circuit in Figure 4. That means fewer losses and higher efficiency.

Figure 5. The proposed multilevel inverter circuit

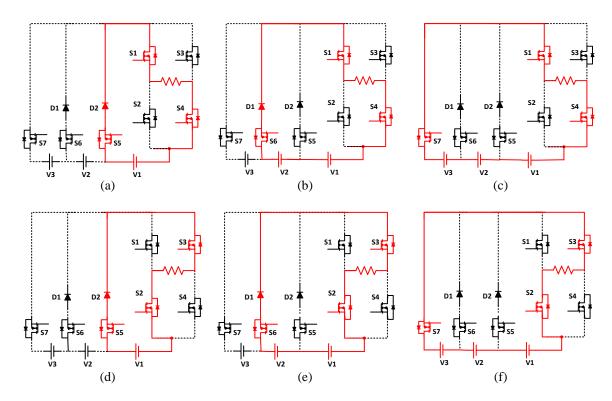

The proposed circuit operates as follows, and only the first 3 modes of operation will be explained as they will be repeated for the rest of the modes:

- At level 1, the load receives energy from the DC source V1 via the switch S5 and the diode D2 on a positive half-cycle basis. For the H-bridge, S1 and S4 are turned on, as seen in Figure 6(a).

- At level 2, Energy is received by the H-bridge via the switch S6 and D1 from the DC sources V1 and V2. Switches S1 and S4 stay on, as seen in Figure 6(b).

- At level 3, through the switch S7, the H-bridge receives energy from the DC sources V1, V2, and V3. Switches S1 and S4 stay on, as seen in Figure 6(c).

- At level 4, the load receives energy from the DC source V1 via the switch S5 and the diode D2 on a negative half-cycle basis. For the H-bridge, S3 and S2 are turned on, as seen in Figure 6(d).

- At level 5, energy is received by the H-bridge via the switch S6 and D1 from the DC sources V1 and V2. Switches S3 and S2 stay on, as seen in Figure 6(e).

- At level 6, through the switch S7, the H-bridge receives energy from the DC sources V1, V2, and V3. Switches S3 and S2 stay on, as seen in Figure 6(f).

Figure 6. The positive and the negative levels of operation of the proposed inverter (a) level 1, (b) level 2, (c) level 3, (d) level 4, (e) level 5, and (f) level 6

# 4. SIMULATION MODEL & RESULT OF THE PROPOSED INVERTER

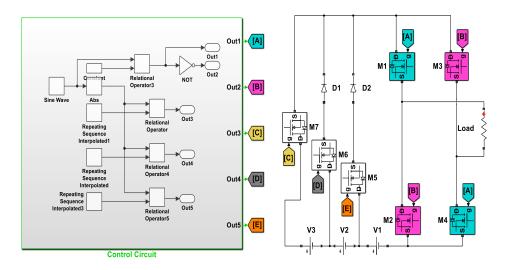

The MATLAB/Simulink model of the proposed inverter is shown in Figure 7. The control circuit generates the gate signals for the switches by comparing a three-phase, 12,250 Hz triangular carrier signal with a 50 Hz sinusoidal reference signal, which is accomplished through the use of the PWM approach. The waveforms of the control circuit are illustrated in Figure 8.

Figure 7. The simulink model of the proposed circuit

Figure 8. The control circuit waveforms of the proposed topology

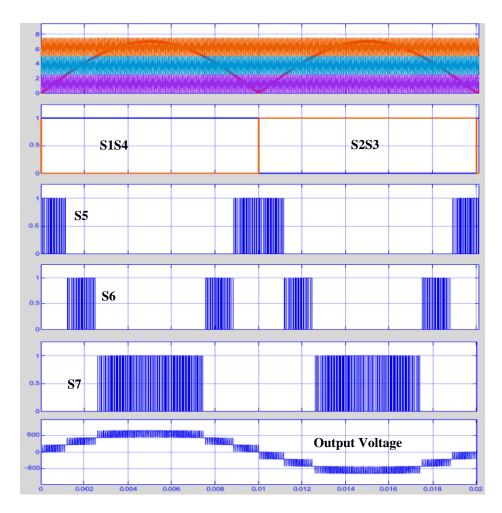

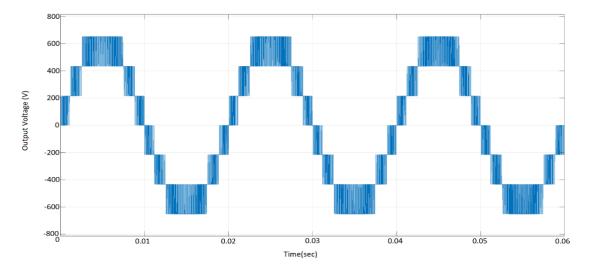

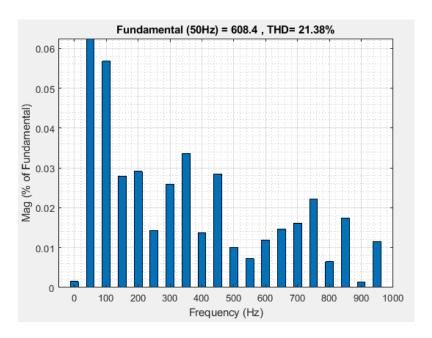

Control pulses for the proposed inverter are generated by a series of logical and mathematical MATLAB functions. Output voltage for the proposed 7-levels inverter is shown in Figure 9. The THD for the output voltage is shown in Figure 10, and it can be seen that the THD is about 21.38 when the modulation index m is 0.95.

Figure 9. The output voltage of the proposed topology

Figure 10. The THD of the proposed topology

For the proposed topology, the number of levels is 7, and for comparison with the inverter circuit that was explained in section c of the previous section, the number of switches is the same. Yet, in the proposed circuit, each level requires one diode and one switch to be in conduction mode. Table 1 shows a comparison between the number of switches in the different topologies for seven-level inverters:

Table 1. The number of switches in the different topologies for seven level inverters

|                          | a-circuit | b-circuit | c-circuit | Proposed circuit |

|--------------------------|-----------|-----------|-----------|------------------|

| Number of power switches | 9         | 7         | 7         | 7                |

| Number of diodes         | 0         | 2         | 2         | 2                |

674 🗖 ISSN: 2302-9285

The reduction in switches used leads to a reduction in the size, weight, and cost and an improvement in the efficiency of the converter. The efficiency is also affected by the number of switches in conduction mode in each level of operation. Table 2 shows a comparison between the number of switches during the on-state in the first three levels of operation for the different circuits shown in the previous section.

| TD 1 1 0 TD1 1      | C ', 1         |              | 1            | .1 1 1       | c            |

|---------------------|----------------|--------------|--------------|--------------|--------------|

| Table 2. The number | er of switches | s in on-mode | in the first | three levels | of oneration |

| 1 aoic 2. The humbe | of Switcher    | o m on mouc  | m me mot     | unice ievens | or operation |

|         | a-circuit    |       | b-circuit    |       | c-circuit    |       | Proposed circuit |       |

|---------|--------------|-------|--------------|-------|--------------|-------|------------------|-------|

|         | Power switch | diode | Power switch | diode | Power switch | diode | Power switch     | diode |

| Level 1 | 5            | -     | 3            | 2     | 3            | 2     | 3                | 1     |

| Level 2 | 5            | -     | 4            | 1     | 3            | 1     | 3                | 1     |

| Level 3 | 5            | -     | 5            | 0     | 3            | 0     | 3                | 0     |

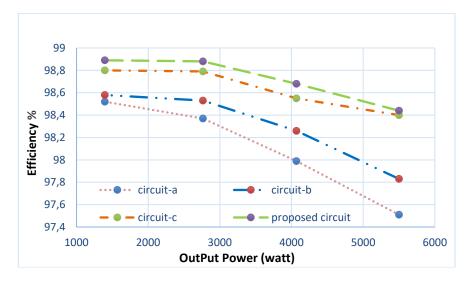

From Table 2, it can be seen that c-circuit and the proposed circuit have the lowest number of switching devices during the on state. On the other hand, the proposed circuit has only one diode working in each operating mode. The reduction of the number of switches (on-state) in the inverter during the operation modes, as well as the reduction of the on-mode, leads to an increase in efficiency. The effect of the switch reduction becomes more significant when adopting a higher number of levels of output voltage. Figure 11 shows the efficiency comparison for the four topologies adopted in this article. This figure shows that the highest efficiency was obtained in the proposed circuit.

Figure 11. The efficiency comparison

### 5. CONCLUSION

In today's applications, MLIs are becoming increasingly important. The proposed inverter has the potential to produce a high-quality output voltage while minimizing losses and increasing efficiency. It outperforms the traditional cascaded multilevel inverter in terms of performance. Switching losses are reduced when the suggested control strategy is used, resulting in increased efficiency. According to the simulation results, the new topology is more efficient than the previous inverters.

## REFERENCES

- [1] M. Samy, M. Mokhtar, N. H. Saad, and A. A. El-Sattar, "Modified hybrid PWM technique for cascaded MLI and cascaded MLI application for DTC drive," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 13, no. 1, p. 47, Mar. 2022, doi: 10.11591/ijpeds.v13.i1.pp47-57.

- [2] A. Prayag and S. Bodkhe, "A comparative analysis of classical three phase multilevel (five level) inverter topologies," in 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Jul. 2016, doi: 10.1109/icpeices.2016.7853567.

- [3] R. K. Antar, T. A. Hussein, and A. M. Abdullah, "Design and implementation of reduced number of switches for new multilevel inverter topology without zero-level state," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 13, no. 1, p. 401, Mar. 2022, doi: 10.11591/ijpeds.v13.i1.pp401-410.

- [4] S. Maurya, D. Mishra, K. Singh, A. K. Mishra, and Y. Pandey, "An Efficient Technique to reduce Total Harmonics Distortion in Cascaded H- Bridge Multilevel Inverter," in 2019 IEEE International Conference on Electrical, Computer and Communication Technologies (ICECCT), Feb. 2019, doi: 10.1109/icecct.2019.8869424.

- [5] A. Kahwa, H. Obara, and Y. Fujimoto, "Design of 5-level reduced switches count H-bridge multilevel inverter," *IEEE 15th International Workshop on Advanced Motion Control (AMC)*, pp. 41–46, Mar. 2018, doi: 10.1109/amc.2019.8371060.

- [6] A. K. Koshti and M. N. Rao, "A brief review on multilevel inverter topologies," in 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), Feb. 2017, doi: 10.1109/icdmai.2017.8073508.

- [7] G. D. Prasad, V. Jegathesan, and P. V. V. R. Rao, "Hybrid multilevel DC link inverter with reduced power electronic switches," *Energy Procedia*, vol. 117, pp. 626–634, Jun. 2017, doi: 10.1016/j.egypro.2017.05.162.

- [8] P. Roseline, B. Ramesh, and Ch. V. V. M. Lakshmi, "Performance analysis of twenty seven level asymmetrical cascaded h-bridge multi level inverter fed three phase induction motor drive," *International Journal of Engineering and Advanced Technology* (*IJEAT*), vol. 4, no. 1, pp. 23–28, Oct. 2014.

- [9] H. Katir, A. Abouloifa, K. Noussi, and I. Lachkar, "Adaptive backstepping control of cascaded h-bridge multilevel DC/AC converters," in 2019 4th World Conference on Complex Systems (WCCS), Apr. 2019, doi: 10.1109/icocs.2019.8930727.

- [10] L. Nanda, C. Jena, A. Pradhan, and B. Panda, "A proposed asymmetrical configuration of cascaded multilevel inverter topology for high level generation," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 13, no. 1, p. 289, Mar. 2022, doi: 10.11591/ijpeds.v13.i1.pp289-297.

- [11] S. S. A. Dangeti, C. K. P. Sekharamantry, V. K. Bayanti, B. A. R. Ch, K. R. Murthy, and A. Tirupathi, "A cascaded converter using hybrid cells and H-bridge structure," *Bulletin of Electrical Engineering and Informatics*, vol. 10, no. 6, pp. 2972–2979, Dec. 2021, doi: 10.11591/eei.v10i6.2783.

- [12] K. Odo, C. Ohanu, I. C-Ogbuka, A. Ajibo, C. Ogbuka, and E. Ejiogu, "A novel direct torque and flux control of permanent magnet synchronous motor with analytically-tuned PI controllers," *International Journal of Power Electronics and Drive Systems* (IJPEDS), vol. 12, no. 4, p. 2103, Dec. 2021, doi: 10.11591/ijpeds.v12.i4.pp2103-2112.

- [13] A. A. Saleh, R. K. Antar, and H. A. Al-Badrani, "Design of new structure of multilevel inverter based on modified absolute sinusoidal PWM technique," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 12, no. 4, p. 2314, Dec. 2021, doi: 10.11591/ijpeds.v12.i4.pp2314-2321.

- [14] K. M. Abdulhassan and O. Y. K. Al-Atbee, "Improved modified a multi-level inverter with a minimum total harmonic distortion," Bulletin of Electrical Engineering and Informatics, vol. 11, no. 2, pp. 672–680, Apr. 2022, doi: 10.11591/eei.v11i2.3466.

- [15] V. A. Kumar and A. Mouttou, "Improved performance with fractional order control for asymmetrical cascaded H-bridge multilevel inverter," *Bulletin of Electrical Engineering and Informatics*, vol. 9, no. 4, pp. 1335–1344, Aug. 2020, doi: 10.11591/eei.v9i4.1885.

- [16] M. A. Hutabarat, S. Hasan, A. H. Rambe, and S. Suherman, "Design and simulation hybrid filter for 17 level multilevel inverter," Bulletin of Electrical Engineering and Informatics, vol. 9, no. 3, pp. 886–897, Jun. 2020, doi: 10.11591/eei.v9i3.890.

- [17] P. Anusha and B. V. Rajanna, "Induction drive system with DSTATCOM based asymmetric twin converter," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 11, no. 4, p. 1826, Dec. 2020, doi: 10.11591/ijpeds.v11.i4.pp1826-1834.

- [18] C. R. Balamurugan and K. Vijayalakshmi, "Comparative Analysis of Various Z-source Based Five Level Cascaded H-bridge Multilevel Inverter," *Bulletin of Electrical Engineering and Informatics*, vol. 7, no. 1, pp. 1–14, Mar. 2018, doi: 10.11591/eei.v7i1.656.

- [19] M. M. A. Alakkad, Z. Rasin, M. Rasheed, W. A. Halim, and R. Omar, "Real-time switching thirteen-level modified CHB-Multilevel inverter using artificial neural network technique based on selective harmonic elimination," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 20, no. 3, p. 1642, Dec. 2020, doi: 10.11591/ijeecs.v20.i3.pp1642-1652.

- [20] H. Chadli, S. Chadli, M. Boutouba, M. Saber, and A. Tahani, "Hardware implementation and performance evaluation of microcontroller-based 7-level inverter using POD-SPWM technique," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 23, no. 1, p. 120, Jul. 2021, doi: 10.11591/ijeecs.v23.i1.pp120-131.

- [21] M. A. I. A. Jewari, A. Jidin, S. A. A. Tarusan, and M. Rasheed, "Implementation of SVM for five-level cascaded H-Bridge multilevel inverters utilizing FPGA," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 11, no. 3, p. 1132, Sep. 2020, doi: 10.11591/ijpeds.v11.i3.pp1132-1144.

- [22] H. Mhiesan, S. S. Lee, Y. Wei, and A. Mantooth, "A New Family of 7-Level Boost Active Neutral Point Clamped Inverter," in 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2019. doi: 10.1109/wipda46397.2019.8998804.

- [23] Kamaldeep and J. Kumar, "A new 7-level asymmetrical multilevel inverter with reduced number of sources and switching components," in 2016 7th India International Conference on Power Electronics (IICPE), Nov. 2016. doi: 10.1109/iicpe.2016.8079497.

- [24] M. E. Ahmad, A. H. Numan, and D. Y. Mahmood, "Enhancing performance of grid-connected photovoltaic systems based on three-phase five-level cascaded inverter," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 12, no. 4, p. 2295, Dec. 2021, doi: 10.11591/ijpeds.v12.i4.pp2295-2304.

- [25] M. A. gabalawy, R. M. Hossam, S. A. Hussien, and N. S. Hosny, "Switched capacitor based multi-level boost inverter for smart grid applications," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 11, no. 5, p. 3772, Oct. 2021, doi: 10.11591/ijece.v11i5.pp3772-3781.

- [26] R. Anand and M. Kamatchi, "A Fifteen Level Cascaded H-Bridge Multilevel Inverter with Space Vector PWM Technique with Reduced Number of Switches," *International Journal of Information and Technology (IJIT)*, vol. 2, no. 3, pp. 41–53, 2016.

- [27] M. Q. Kasim and R. F. Hassan, "Active voltage balancing strategy of asymmetric stacked multilevel inverter," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 23, no. 2, p. 665, Aug. 2021, doi: 10.11591/ijeecs.v23.i2.pp665-674.

- [28] S. Umashankar, T. S. Sreedevi, V. G. Nithya, and D. Vijayakumar, "A New 7-Level Symmetric Multilevel Inverter with Minimum Number of Switches," ISRN Electronics, vol. 2013, pp. 1–8, Aug. 2013, doi: 10.1155/2013/476876.

- [29] U. Gajula, "Reduced Switch Multilevel Inverter Topologies And Modulation Techniques For Renewable Energy Applications," Turkish Journal of Computer and Mathematics Education (TURCOMAT), vol. 12, no. 3, pp. 4659–4670, Apr. 2021, doi: 10.17762/turcomat.v12i3.1879.

676 Signature 185N: 2302-9285

## **BIOGRAPHIES OF AUTHORS**

Osama Yaseen Khudair Al-Atbee si a Lecturer at the Department of Electrical Engineering at the University of Basrah, Iraq, where he has been a faculty member since 2006. Osama graduated from the Engineering College/Department of Electrical Engineering in 2001 from the University of Basrah and got his Msc in 2005 from the same university. In 2018, he got his Ph.D in Electrical Engineering from the Engineering College, University of Leicester, United Kingdom (UK). His research interests are primarily in the areas of renewable energy, power electronics, and micro-grids. He can be contacted at email: usama.khader@uobasrah.edu.iq.

Khalid M. Abdulhassan received his B.Sc degree in electrical engineering from the Engineering College at the University of Basrah in 1997. He received his Master's degree from the same university in 2001. In 2011, He got his Ph.D from the Engineering College/Department of Electrical Engineering /University of Basrah, Iraq. He is now a faculty member at the engineering college at the University of Basrah, Iraq. His research interests include control strategies for AC and DC machines and power electronics. He can be contacted at email: Khalid.abdulhassan@uobasrah.edu.iq.