ISSN: 2302-9285, DOI: 10.11591/eei.v12i1.4128

# Performance parameters optimization of CMOS analog signal processing circuits based on smart algorithms

# Israa Mohammed Rasheed<sup>1,2</sup>, Hassan Jasim Motlak<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, College of Engineering, University of Babylon, Hillah, Iraq <sup>2</sup>Department of Computer Technical Engineering, College of Technical Engineering, The Islamic University, Najaf, Iraq

# **Article Info**

## Article history:

Received May 24, 2022 Revised Sep 5, 2022 Accepted Oct 12, 2022

### Keywords:

CMOS CCII

CMOS FCOTA

CMOS OTA

Op-amps

Operational transconductance

amplifier

# **ABSTRACT**

Designing ideal analogue circuits has become difficult due to extremely large-scale integration. The complementary metal oxide semiconductor (CMOS) analog integrated circuits (IC) could use an evolutionary method to figure out the size of each device. The CMOS operational transconductance amplifier (CMOS OTA) and the CMOS current conveyor second generation (CMOS CCII) are designed using advanced nanometer transistor technology (180 nm). Both CMOS OTA and CMOS CCII have high performance, such as a wide frequency, voltage gain, slew rate, and phase margin, to include very wide applications in signal processing, such as active filters and oscillators. The optimization approach is an iterative procedure that uses an optimization algorithm to change design variables until the optimal solution is identified. In this study, different sorts of algorithms the genetic algorithm (GA), particle swarm optimization (PSO), and cuckoo search (CS) are employed to boost and enhance the performance parameters. While decreasing the time required to develop a conventional operation amplifier's settling time. Some studies decrease the value of the power utilized at various frequencies. Others operate at extremely high frequencies, but their power consumption is greater than that of those operating at lower frequencies.

This is an open access article under the <u>CC BY-SA</u> license.

149

# Corresponding Author:

Israa Mohammed Rasheed

Department of Electrical Engineering, College of Engineering, University of Babylon

Hillah, Iraq

Email: engisraajadui95@gmail.com

#### 1. INTRODUCTION

The two main types of integrated circuits (IC) implementation are bipolar and complementary metal oxide semiconductor (CMOS) [1]. In comparison to CMOS technology, bipolar technology is known for having lower noise, better performance at high frequencies, and greater transconductance [2], [3]. Bipolar technology is better than CMOS technology because it has a higher input resistance, uses less power, and can be made on a smaller area of silicon [4]. Using CMOS technology to make an IC is an art form in the field of electronics [5].

Analog IC designers could, for instance, use simulators of circuits such as simulation software with an IC emphasis (SPICE) to evaluate electrical qualities that can be enhanced by adjusting CMOS transistor sizes, and this can be done using an optimization strategy [5], [6]. Increasing CMOS amplifier slew rate, decreasing noise, power, voltage, and layout area, CMOS power gain and other forms of improvement [7], [8]. One of the most important and fundamental things about CMOS is that it can process information very quickly, especially in versions made with modern technology at 180 nanometers, 350 nanometers, and

Journal homepage: http://beei.org

150 ☐ ISSN: 2302-9285

130 nanometers, as well as its small size, low energy use, and other important characteristics and factors [9]–[11].

In previous years, the bipolar operational transconductance amplifier (OTA) was launched commercially [12]. In both open and closed loop electrical circuits, CMOS OTA has emerged as a crucial component [13]. Operational Transparency According to their input and output, amplifiers are categorized into four groups [14]. The OTA with a single input and a single output, OTA with a differential input, and OTA with a balanced input and differential output [15], [16]. In addition, the current mode technique offers more potential, a wider dynamic range, a simpler circuit design, the lowest power consumption, and a wider signal bandwidth than the voltage mode approach, owing towards its enhanced linearity (bipolar and CMOS technologies) to establish the existing transport circuits [3], [4].

In the sector of analog communications signal processing, current conveyor (CC) circuits are gradually replacing operational amplifiers (op-amps) [17], [18]. Current conveyor second generation (CCII) is a well-known current mode circuit utilized in several applications, including filters and oscillators. In terms of low power consumption, high gain, and other essential characteristics, the work of CMOS amplifiers manufactured using contemporary technologies yields favorable results; nevertheless, this parameter can be enhanced by using methods that have never been utilized in this field before [8], [19]. Using circuit simulators such as SPICE and MATLAB to evaluate the electrical features associated with CMOS technology, metaheuristics have been shown to be beneficial for enhancing analog IC [20]–[22]. The performance parameters of different CMOS OTAs and CMOS CCIIs designs were summarized in this paper. The comparsion of these designs illustrates that low consumption power and wide bandwidth product could be obtained using 0.18 μm CMOS technology and algoritmic process.

#### 2. FUNDAMENTAL OF FOLDED CASCADE CMOS OTA

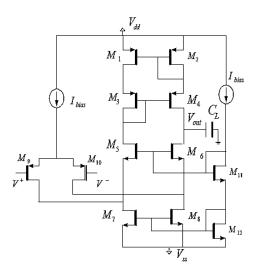

The Op-amps are advantageous for applications with low frequency, such as video and audio systems [6]. Many analog and mixed-signal circuits, such as Gm-C filters, data converters, regulators, and other high-frequency applications, employ the CMOS OTA as a fundamental building block [23]. Optimising analog IC, especially OTA, remains the most fascinating and demanding task in the world of circuit design [24]. The ideal CMOS OTA is a voltage-controlled current source with constant transconductance and infinite input and output impedances, an example of an OTA is the folded cascade OTA (FCOTA) [10]. Figure 1 illustrates the FCOTA circuit layout (6). It consists of two stages: an NMOS differential pair input stage and a cascade output stage.

Figure 1. The CMOS OTA folding cascade architecture [25]

An ideal transconductance amplifier is a voltage-controlled current source with infinite input and output impedance that can drive tiny capacitive loads at high frequencies and has an infinite bandwidth [6]. High linearity, high frequency, and low power are the major issues of CMOS OTA [26]. For various purposes, a number of CMOS OTAs with various topologies have been documented [27]. The CMOS FCOTA has a DC gain >80 dB, unity-gain frequency >200 MHz, slew rate >100 V/s, phase margin >50 o,

and a power consumption of 3. The value of the passive components (capacitors and resistors), the length and width of the transistor, and the bias current magnitude and bias voltages are all design factors [19].

DC in an open loop gain

The open-loop voltage gain of a two-stage op-amp is given by (1):

$$A_V = \frac{g_{M1}}{g_{ds2} + g_{ds4}} \cdot \frac{g_{M6}}{g_{ds7} + g_{ds6}} \tag{1}$$

the transconductance of transistors M1 and M6 are  $g_{M1}$  and  $g_{M6}$ . The output conductance is  $g_{ds2}$ , the transistors transconductance output of (M2, M4, and M7) is  $g_{ds2}$ ,  $g_{ds4}$ ,  $g_{ds7}$ . Respectively.

# - Bandwidth-gain

The gives the unity-gain bandwidth (2):

$$GBW = \frac{g_{m1}}{C_C} \tag{2}$$

where Cc is the capacitance of compensation.

#### Phase margin

The total of phase shifts provided by the no dominating poles (p1 and p2) and zeros (z) at the unity-gain frequency determines the phase margin of an operational amplifier (3):

$$PM = \mp 180 - \tan^{-1}\left(\frac{GBW}{p1}\right) - \tan^{-1}\left(\frac{GBW}{p2}\right) - \tan^{-1}\left(\frac{GBW}{z}\right)$$

(3)

Slew rate

The slew rate of this operational amplifier is given by (4):

$$SR = \frac{I_5}{Cc} \tag{4}$$

where  $I_5$  denotes the current flowing through the transistor M5.

# Power consumption

The power consumption of a two-stage operational amplifier has the form (5):

$$P = (V_{DD} - V_{SS})(I_5 + 2I_7) (5)$$

where  $V_{SS}$  and  $V_{DD}$  are the operational amplifiers power supply and  $I_7$  is the current that flows through transistor M7.

## Area

The sum of the transistor and capacitor areas determines the operational amplifier's area A (6):

$$Area = \sum_{i=1}^{k} W_i \cdot L_i \, 0 \tag{6}$$

where  $W_i$  and  $L_i$  are lengths and widths of MOSFET gate transistors [19].

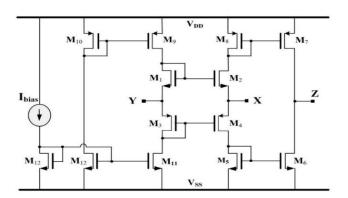

# 3. FUNDAMENTAL OF CMOS CCII

Figure 2 depicts a current conveyor with three active ports: X, Y, and Z. Its primary purpose is to generate a current follower between ports Z and X using the translinear loop formed by transistors M1-M4 [28]. Current mirrors M5-M6 and M7-M8 can be used to create a voltage follower between ports Y and X. The current conveyor topology is the most preferred due to its higher performance and the need to implement a translinear loop [29]. As a consequence, the optimization of the CCII's design takes into account its primary functions: parasitic resistance at port  $X(R_X)$  and cutoff frequency (f-3dB) [30]. Remember that the purpose is to get low input resistance by lowering the first objective and large bandwidth by optimizing the second [31]. L and W is the length of channel and width of gate respectively are the geometrical dimensions that define all transistors. The design challenge can be stated as follows:  $R_X(X)$  and  $f_{-3dB}(X)$  (7).

152 ☐ ISSN: 2302-9285

$$X = \{W_n, W_n, L_n, L_n, I_0\} \tag{7}$$

subject to (8):

$$g_{1,2}(X) \le 0 \tag{8}$$

the resistance  $R_X$  is (9):

$$R_X = \frac{1}{g_{mn} + g_{mp}} = \frac{1}{\sqrt{2\mu_n C_{ox} \frac{W_n}{L_n} I_0} + \sqrt{2\mu_p C_{ox} \frac{W_p}{L_p} I_0}}$$

(9)

where  $g_{mn}$  and  $g_{mp}$  the NMOS and PMOS transistors transconductances respectively,  $C_{ox}$  is the gate oxide capacitance. The bias current is  $I_0$ .  $\mu_n$  the electrons mobility and  $\mu_p$  the holes mobility.

The cut-off frequency is (10):

$$f_{-3dB}(X) = \frac{\omega_{-3dB}}{2\pi} \tag{10}$$

The saturation constraints are  $g_1$  and  $g_2$  are shown in by:

The constraint of M2 and M8 transistors (11):

$$g_1 = V_{SS} - V_X(min) + V_{tn} + \sqrt{\frac{2I_0}{\mu_n C_{ox} \frac{W_n}{L_n}}} + \sqrt{\frac{2I_0}{\mu_p C_{ox} \frac{W_p}{L_p}}}$$

(11)

The constraint of M4 and M5 transistors (12):

$$g_2 = V_X(max) - V_{DD} - V_{tp} + \sqrt{\frac{2I_0}{\mu_n c_{ox} \frac{W_n}{L_n}}} + \sqrt{\frac{2I_0}{\mu_p c_{ox} \frac{W_p}{L_p}}}$$

(12)

The threshold voltage of (NMOS), (PMOS), and supply voltages are  $(V_{tn})$ ,  $(V_{tp})$ ,  $(V_{DD})$ ,  $(V_{SS})$  respectively and  $W_n$   $(W_p)$ ,  $L_n(L_p)$ . Are the gate width and the length of channel for (p channel) (n-channel) transistor, respectively. The  $V_X(min)$ ,  $V_X(max)$  is the minimum and maximum value of voltage. These is mathmetical for CMOS current conveyor second generator CCII. After this the famus algorithm that it used with such tequique is discussed.

Figure 2. CMOS current conveyor second generator CCII [32]

# 4. SMART ALGORITHMS

One important way to improve many performance parameters, like unit product gain, reducing power consumption, and slew rate, is to use smart algorithms [5], [33]. Based on these algorithms can be performance parameters optimization of CMOS analog signal processing circuits. The main ones are the particle swarm optimization (PSO) and cuckoo search (CS) algorithms. Which have high performance of some parameter.

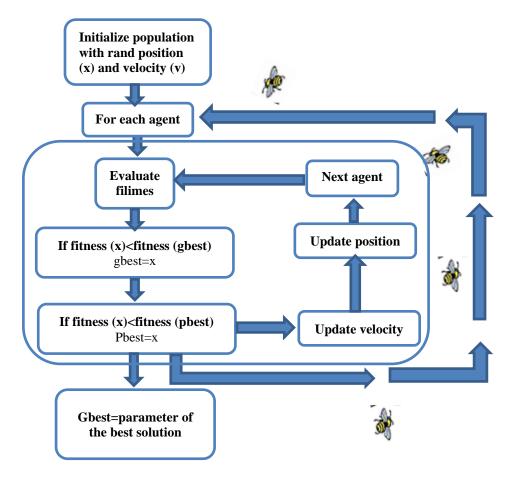

# 5. PARTICLE SWARM OPTIMIZATION ALGORITHM

The social behavior of fish and birds is described by a mathematical model based on the basic properties used to describe complex systems of self-regulation [12], [34]. This model was developed by Kennedy and Eberhart in 1995 and called PSO. Currently, the PSO is used to solve optimization problems significantly and successfully because of a single goal algorithm [15]. The PSO algorithm is represented by a finite search space that contains a set of randomly distributed particles that have a certain velocity and position that are represented by simple mathematical models. These models represent every movement of the particles to be the best place in the search space or the best place as an individual, in addition, there are different rules for updating different variables [35]. The main idea is to provide a search space containing an array of particles, and in addition to setting the initial velocity vector, it gives them a suitable initial position [36]. Depending on certain parameters randomly in order to set the velocity, and during this process, the particle position is changed in each iteration [27]. Each particle has the ability to determine best position and whether its current location is superior to the positions of other particles. According to the math in (13) and (14), the positions and speeds of the particles must be changed based on what is shown in Figure 3.

$$vi(t+1) = vi(t) + c1rand()(pbest(t) - pi(t)) + c2rand()(gbest(t) - pi(t))$$

(13)

$$pi(t+1) = pi(t) + vi(t+1)$$

(14)

where pi (t+1) and vi (t+1) represent the particle position and velocity in the ith iteration, respectively. A function that returns the value of a real random regular number between 0 and 1 is rand (). gbest and pbest represent the best global position among all the particles and the particles' best position; c1 and c2 are parameters representing the particle dependence (perception) and social behavior in the swarm, respectively. These constants are the most closely related in (13), and as shown a number of tests have shown that the convergence is faster the higher the value of the constants [37]. The values of c1 and c2 are important in improving performance depending on the type of problem. The best performance of the PSO algorithm is if the value of the constants c1=c2=2 is set as shown in Figure 3 [6], [15].

Figure 3. The PSO algorithm flowchart [34]

154 □ ISSN: 2302-9285

#### 6. CUCKOO SEARCH ALGORITHM

The CS algorithm is comparable to other algorithms, such as differential evolution (DE), PSO, and genetic algorithm (GA) which are classified as being random [4], [6], [38]. It is one of the algorithms that rely heavily on population. In this algorithm, each individual element is connected to the cuckoo egg, and each pattern is associated with the nest [39]. This algorithm uses a special approach that is similar to the HS algorithm, in which the mechanism of selection or elitism is utilized [40]. Based on several typical measurement functions, the CS algorithm was proposed, and its performance was compared to that of the PSO and DE algorithms in [11], [37]. In randomization, the performance of the CS algorithm was shown to be superior to that of the DE and PSO algorithms [34], [41]. In addition, the researchers observed that the number of parameters that the CS algorithm must adjust is far lower than the number of parameters required by other types of algorithms [42]. The common operation of the CS algorithm is represented by the following (15):

$$Xg + 1, i = Xg, i + \alpha \otimes L\acute{e}vy(\lambda)$$

(15)

Here, the  $i^{th}$  cuckoo of the current solution is  $X_g$  of iteration g,  $X_{g+1,i}$  is the  $i^{th}$  cuckoo of the new solution, and g is the current generation number [36], [39].  $\alpha$  is the size of step which depends on interests problem scales. Lévy( $\lambda$ ) is a random path generated by Lévy flight, and Lévy is obtained from a Lévy distribution with an infinite mean and an infinite variance, as shown in (16) [43]. The random walk algorithm is more efficient than the PSO algorithm. "Product" refers to the multiplication performed inside [10], [44].

$$L\acute{e}vy \sim u = t - \lambda \tag{16}$$

where u is normal distribution and t is CS generation,  $\lambda$  is considered in the range (1, 3). The Mantegna algorithm is used to produce the Lévy path. Following a random walk is the size of the steps [45]. With a force law distribution featuring heavy tails [27].

## 7. LITRECHURE REVIEW

The following Tables 1-3 illustrates the OTA's performance for the years (2012-2021) with and without using various algorithms, and for overall references from 2012–2022 of CCII. These tables content important parameters with are used in high frequency application, as DC gain (dB), bandwidth of unity gain (MHz), phase margin (degree), type of algorithm, slew rate(mV/ $\mu$ s), chip area  $\mu$ m², consumption power mw, and technology (channel length) ( $\mu$ m). In Table 1, there are numerous publications, each of which focuses on or is interested in a specific aspect, such as power consumption, slew rate, and gain bandwidth product. To reduce power consumption, the authors in [9] employs the CS algorithm, where power consumption is as low as possible compared to other research. As for bandwidth, the search results using the PSO algorithm are excellent, and packets have been significantly enhanced in [2]. The majority of research uses high frequencies at the expense of energy.

Table 2 displays the research group that does not employ a specific algorithm. The lowest value of energy consumed was 144.3 nanowatts in 2010 study, and the maximum bandwidth they were able to achieve was 485 MHz in 2013. Several researches are listed in Table 3, some of which depend on a certain type of algorithms and others on the sort of technology used to nationalize the system. In comparison to other studies, research conducted in 2013 is regarded as the most effective in terms of reducing energy consumption.

Table 1. Presented a summary of the performance parameters of several types of CMOS OTA designs based

on algorithmic processes for the years 2012-2020 Chip Consump-Refrences DC Bandwidth Phase Type of Slew rate Technology gain of unity margin algorithm  $(mV/\mu s)$ (channel len-Area tion (dB) gain (MHz power mw gth) (µm) (degree)  $\mu m^2$ MOGA 2.25 Samir Barra et al. [1] 0.047 96 70° 89 0.1851.34° B.Mohammad et al. [2] 84.33 543.3 **PSO** 534 1.2 0.18 Benhala and Ahaitouf [9] 85.58 GA3.676 5.23 0.5 1.5 70° 559 0.047 MOGA 2250 0.18 Dendouga et al. [12] 76 63.53° Prajapati and Shah [13] 59.19 20.03 **PSO** 18350 28.52 0.184 0.18 Prajapati and Shah [13] 50.49 16.38 50.09° **PSO** 20130 97.81 0.349 0.35 Prajapati and Shah [14] 91.39 0.14555 68.87° **PSO** 11900 4839.8 0.01492 0.18 3155 Motlak and Mohammed [15] 89.6° **PSO** 0.485 82. 6.27 Salhi et al. [16] 88.95 83.653 55.202 IWO 27.5 0.5796 Prajapati and Shah [17] 76.17 0.02021 45.43° CS 22060 5409.4 0.000278 0.18 Prajapati and Shah [17] 85.04 0.06004 73.69° CS 12430 3458 0.000863 0.35

| Table 2. Different ( |  |  |

|----------------------|--|--|

|                      |  |  |

|                      |  |  |

|                             | DC    | Bandwidth  | Phase    | Slew         | Chip     | consumption | Technology       |

|-----------------------------|-------|------------|----------|--------------|----------|-------------|------------------|

| Refrences                   | gain  | of unity   | margin   | rate         | area     | power       | (channel length) |

|                             | (dB)  | gain (MHz) | (degree) | $(mV/\mu s)$ | $(mm^2)$ | (mW)        | (µm)             |

| Mukahar and Jubadi [20]     | 48.8  | 9.32       |          |              | 0.089    | 4.88        | 0.5              |

| Pereira-Arroyo et al. [44]  |       |            |          | 3.676        |          | 0. 1443     |                  |

| Laajimi et al. [45]         | 57    | 55         | 62°      | 0.1          |          | 2.27        |                  |

| Bakawale et al. [30]        |       |            | 55°      |              | 0.025    | 14.2        |                  |

| Lee et al. [46]             | 87    | 485        | 70°      |              |          | 8           | 0.35             |

| Yodtean [37]                | 76    | 423        | 86°      |              | 0.4      | 0.00458     | 0.18             |

| Mirković et al. [47]        | 57.6  | 140        | 83°      | 190000       |          | 9.77        | 0.350            |

| Daoud et al. [26]           | 46    | 14         | 85°      |              |          | 0.028       | 0.18             |

| Abdelfattah et al. [48]     | 46    | 3.6        | 56°      |              |          |             | 0.35             |

| Akbari and Hashemipour [38] | 96    | 11         | 76°      | 96           |          | 0.4         | 0.18             |

| Garradhi et al. [43]        | 42.58 | 247.3      | 92°      |              |          | 0.5         | 0.090            |

| Yang and Roberts [49]       | 52    | 4,8        | 57°      | 5            |          | 3.72        | 130              |

| Patel and Thakker [27]      | 44.5  | 18.7       | 60.5°    |              |          |             |                  |

| Sabry <i>et al</i> . [50]   | 32    | 3.95       | 70°      |              |          |             | 0.18             |

| Dong et al. [51]            |       | 9.76       | 71.7°    | 2.76         | 0.213    | 29.46       |                  |

Table 3. Illustrate the overall references from 2012–2022 of CCII

| Refrences               | Type of algorithms | Technology<br>(channel length) (μm) | Supply<br>voltage (V) | Bias<br>current (μA) | Maximum<br>frequency (MHz) | Consumption power (mW) |

|-------------------------|--------------------|-------------------------------------|-----------------------|----------------------|----------------------------|------------------------|

| Bakawale et al. [30]    |                    |                                     | 1.12                  |                      | 25                         | 14.2                   |

| Broomandnia et al. [31] |                    | 0.18                                | ±0.6                  |                      | 0.006                      | 0.191                  |

| Gajjar and Patel [32]   |                    | 0.18                                | 1.8                   | 4                    |                            | 0.070                  |

| M'Harzi et al. [52]     |                    | 0.35                                | ±1.5                  | 100                  |                            | 1.28                   |

| Garbaya et al. [53]     | RBF-PSO            |                                     |                       |                      |                            |                        |

| Yakout and Alawadi [54] |                    | 0.8                                 | $\pm 2.5$             | 300                  |                            | 4.86                   |

| Lberni et al. [55]      | NSGA II            | 0.18                                | $\pm 1.8$             | 80                   | 6600                       |                        |

|                         | and MOGA           |                                     |                       |                      |                            |                        |

| Mallick et al. [56]     | CRPSO              | 0.18                                | ±2.5                  |                      |                            |                        |

## 8. CONCLUSION

Numerous applications utilize high frequencies, and compared to low frequencies, their power consumption is greater; however, some studies underestimate the power consumed at various frequencies. High bandwidth, phase margin, spin rate, and voltage gain, which are performance parameters for CMOS OTA and CMOS CCII. This parameter was enhanced by the use of cutting-edge (180 nm) nanoscale transistor technology. Second, different types of algorithms such as CS, PSO, and GA are utilized. Using PSO, the maximum bandwidth available is equal to 543.3 MHz. The minimum power consumption in CMOS OTA is 278 uW, whereas in CMOS CCII it is 70 uW.

### REFERENCE

- [1] S. Barra, A. Dendouga, S. Kouda, and N.-E. Bouguechal, "Multi-objective genetic algorithm optimization of CMOS operational amplifiers," in 2012 24th International Conference on Microelectronics (ICM), Dec. 2012, pp. 1–4, doi: 10.1109/ICM.2012.6471451.

- [2] B. Mohammad, P. Dadabhoy, K. Lin, and P. Bassett, "Comparative study of current mode and voltage mode sense amplifier used for 28 nm SRAM," in 2012 24th International Conference on Microelectronics (ICM), Dec. 2012, pp. 1–6, doi: 10.1109/ICM.2012.6471396.

- [3] A. Ezzaki, L. Masmoudi, M. el Ansari, F.-A. Moreno, R. Zenouhi, and J. G. Jimenez, "Edge detection algorithm based on quantum superposition principle and photons arrival probability," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 2, pp. 1655–1666, Apr. 2020, doi: 10.11591/ijece.v10i2.pp1655-1666.

- [4] N. Dib and U. Al-Sammarraie, "Optimal design of symmetric switching CMOS inverter using symbiotic organisms search algorithm," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 1, pp. 171–179, Feb. 2020, doi: 10.11591/ijece.v10i1.pp171-179.

- [5] S. M. Hameed, H. K. AL-Qaysi, A. S. Kaittan, and M. H. Ali, "Evaluation of electrical load estimation in Diyala governorate (Baaquba city) based on fuzzy inference system," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 11, no. 5, pp. 3757–3762, Oct. 2021, doi: 10.11591/ijece.v11i5.pp3757-3762.

- [6] D. R. Sulaiman, "Multi-objective Pareto front and particle swarm optimization algorithms for power dissipation reduction in microprocessors," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 6, pp. 6549–6557, Dec. 2020, doi: 10.11591/ijece.v10i6.pp6549-6557.

- [7] S. Lahiani, H. Daoud, S. ben Selem, and M. Loulou, "Low voltage low power folded cascode OTA design for RF applications," International Journal of Applied Engineering Research, vol. 12, no. 13, pp. 4029–4034, 2017.

- [8] A. el Beqal, B. Benhala, and I. Zorkani, "A Genetic algorithm for the optimal design of a multistage amplifier," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 1, pp. 129–138, Feb. 2020, doi: 10.11591/ijece.v10i1.pp129-138.

- [9] B. Benhala and A. Ahaitouf, "GA and ACO in hybrid approach for analog circuit performance optimization," in 2014 International Conference on Multimedia Computing and Systems (ICMCS), Apr. 2014, pp. 1590–1595, doi: 10.1109/ICMCS.2014.6911344.

156 ☐ ISSN: 2302-9285

[10] K. B. Maji, R. Kar, D. Mandal, and S. P. Ghoshal, "An evolutionary approach based design automation of low power CMOS two-stage comparator and folded cascode OTA," AEU - International Journal of Electronics and Communications, vol. 70, no. 4, pp. 398–408, Apr. 2016, doi: 10.1016/j.aeue.2015.12.019.

- [11] A. J. Khalaf and S. J. Mohammed, "Verification and comparison of MIT-BIH arrhythmia database based on number of beats," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 11, no. 6, pp. 4950–4961, Dec. 2021, doi: 10.11591/ijece.v11i6.pp4950-4961.

- [12] A. Dendouga, S. Oussalah, D. Thienpont, and A. Lounis, "Multiobjective genetic algorithms program for the optimization of an OTA for front-end electronics," *Advances in Electrical Engineering*, vol. 2014, pp. 1–5, Aug. 2014, doi: 10.1155/2014/374741.

- [13] P. P. Prajapati and M. V. Shah, "Two stage CMOS operational amplifier design using particle swarm optimization algorithm," in 2015 IEEE UP Section Conference on Electrical Computer and Electronics (UPCON), Dec. 2015, pp. 1–5. doi: 10.1109/UPCON.2015.7456700.

- [14] P. P. Prajapati and M. V. Shah, "Automated sizing methodology for CMOS miller operational transconductance amplifier," in *Advances in Intelligent Systems and Computing*, 2018, pp. 301–308, doi: 10.1007/978-981-10-5699-4\_29.

- [15] H. J. Motlak and M. J. Mohammed, "Design of self-biased folded cascode CMOS op-amp using PSO algorithm for low-power applications," *International Journal of Electronics Letters*, vol. 7, no. 1, pp. 85–94, Jan. 2019, doi: 10.1080/21681724.2018.1440422.

- [16] S. Salhi, A. Slimane, H. Escid, and S. A. Tedjini, "Design and analysis of CMOS RCG transimpedance amplifier based on elliptic filter approach," *IET Circuits, Devices & Systems*, vol. 12, no. 4, pp. 497–504, Jul. 2018, doi: 10.1049/iet-cds.2017.0449.

- [17] P. P. Prajapati and M. V. Shah, "Automatic circuit design of CMOS miller OTA using cuckoo search algorithm," *International Journal of Applied Metaheuristic Computing*, vol. 11, no. 1, pp. 36–44, Jan. 2020, doi: 10.4018/IJAMC.2020010103.

- [18] R. Pandey, S. Kumar, V. Sonia, P. Singh, S. Ghangas, and S. Bisariya, "A review on CMOS operational transconductance amplifier on different technology node," in 2nd International Conference on "Advancement in Electronics & Communication Engineering (AECE 2022), 2022, pp. 584–587. doi: 10.2139/ssrn.4159096.

- [19] H. Bouyghf, B. Benhala, and A. Raihani, "Analysis of the impact of metal thickness and geometric parameters on the quality factor-Q in integrated spiral inductors by means of artificial bee colony technique," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 9, no. 4, pp. 2918–2931, Aug. 2019, doi: 10.11591/ijece.v9i4.pp2918-2931.

- [20] N. Mukahar, S. H. Ruslan, and W. M. Jubadi, "Operational transconductance amplifier design for A 16-bit pipelined ADC," in Proceedings of EnCon2008 2nd Engineering Conference on Sustainable Engineering Infrastructures Development & Management, 2008, pp. 1026–1031.

- [21] E. Cabrera-Bernal, S. Pennisi, A. D. Grasso, A. Torralba, and R. G. Carvajal, "0.7-V three-stage class-AB CMOS operational transconductance amplifier," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 11, pp. 1807–1815, Nov. 2016, doi: 10.1109/TCSI.2016.2597440.

- [22] J. C. Bansal, P. K. Singh, and N. R. Pal, Evolutionary and swarm intelligence algorithms. Cham: Springer, 2019, doi: 10.1007/978-3-319-91341-4.

- [23] D. S. S. Sam, P. S. Paul, and D. Jayanthi, "A novel architecture of a low power folded cascode OTA in 180nm CMOS process," in 2021 7th International Conference on Advanced Computing and Communication Systems (ICACCS), Mar. 2021, pp. 95–99, doi: 10.1109/ICACCS51430.2021.9441988.

- [24] R. U. Ahmed, E. A. Vijaykumar, H. S. Ponakala, M. Y. V. Balaji, and P. Saha, "Design of double-gate cmos based two-stage operational transconductance amplifier using the utbsoi transistors," *UPB Scientific Bulletin, Series C: Electrical Engineering and Computer Science*, vol. 82, no. 2, pp. 173–188, 2020.

- [25] H. Daoud, S. ben Salem, S. Zouari, and M. Loulou, "Folded cascode OTA design for wide band applications," in *International Conference on Design and Test of Integrated Systems in Nanoscale Technology*, 2006. DTIS 2006., 2006, pp. 437–440. doi: 10.1109/DTIS.2006.1708674.

- [26] M. Shahabi, R. Jafarnejad, J. Sobhi, and Z. D. Kouzehkanani, "A novel low power high CMRR pseudo-differential CMOS OTA with common-mode feedforward technique," in 2015 23rd Iranian Conference on Electrical Engineering, May 2015, pp. 1290–1295, doi: 10.1109/IranianCEE.2015.7146415.

- [27] S. Patel and R. A. Thakker, "Automatic circuit design and optimization using modified PSO algorithm," *Journal of Engineering Science and Technology Review*, vol. 9, no. 4, pp. 192–197, Aug. 2016, doi: 10.25103/JESTR.094.27.

- [28] S. ben Salem, M. Fakhfakh, D. S. Masmoudi, M. Loulou, P. Loumeau, and N. Masmoudi, "A high performances CMOS CCII and high frequency applications," *Analog Integrated Circuits and Signal Processing*, vol. 49, no. 1, pp. 71–78, Oct. 2006, doi: 10.1007/s10470-006-8694-4.

- [29] T. Ettaghzouti, N. Hassen, and K. Besbes, "Novel CMOS second generation current conveyor CCII with rail-to-rail input stage and filter application," in 2014 IEEE 11th International Multi-Conference on Systems, Signals & Devices (SSD14), Feb. 2014, pp. 1–6, doi: 10.1109/SSD.2014.6808800.

- [30] N. Bakawale, M. Jain, and R. S. Gamad, "Design and performance verification of current conveyor based pipeline A/D converter using 180 nm technology," *European Scientific Journal*, vol. 8, no. 27, pp. 118–131, 1857.

- [31] H. Broomandnia, E. Rahimi, and M. H. Danesh, "Optimized design of an improved current mode instrumentation amplifier approaching the ideal one based on bulk driven differential voltage second generation current conveyor," in 5th Iranian Conference on Electrical and Electronic Engineering (ICEEE2013), 2013, pp. 134–139.

- [32] M. K. Gajjar and N. D. Patel, "Analysis of CMOS second generation current conveyors," *International Journal of Engineering Research & Technology (IJERT)*, vol. 3, no. 2, pp. 1464–1467, 2014, doi: 10.17577/IJERTV3IS20947.

- [33] E. B. Asmae, K. Loubna, B. Bachir, and Z. Izeddine, "Meta-heuristic techniques for optimal design of analog and digital filter," Indonesian Journal of Electrical Engineering and Computer Science, vol. 19, no. 2, pp. 669–679, Aug. 2020, doi: 10.11591/ijeecs.v19.i2.pp669-679.

- [34] D. Wang, D. Tan, and L. Liu, "Particle swarm optimization algorithm: an overview," Soft Computing, vol. 22, no. 2, pp. 387–408, Jan. 2018, doi: 10.1007/s00500-016-2474-6.

- [35] E. Barmala, "Design and simulate a doherty power amplifier using GaAs technology for telecommunication applications," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 15, no. 2, pp. 845–854, Aug. 2019, doi: 10.11591/ijeecs.v15.i2.pp845-854.

- [36] S. Abi, H. Bouyghf, B. Bachir, and A. Raihani, "An optimal design of square spiral integrated inductor using metaheuristic techniques," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 20, no. 2, pp. 680–689, Nov. 2020, doi: 10.11591/ijeecs.v20.i2.pp680-689.

- [37] A. Yodtean, "A CMOS OTA and implementation," in 2014 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Dec. 2014, pp. 094–098, doi: 10.1109/ISPACS.2014.7024432.

- [38] M. Akbari and O. Hashemipour, "High gain and high CMRR two-stage folded cascode OTA with nested miller compensation," *Journal of Circuits, Systems and Computers*, vol. 24, no. 4, pp. 1–13, Apr. 2015, doi: 10.1142/S0218126615500577.

- [39] M. Mareli and B. Twala, "An adaptive cuckoo search algorithm for optimisation," Applied Computing and Informatics, vol. 14, no. 2, pp. 107–115, Jul. 2018, doi: 10.1016/j.aci.2017.09.001.

- [40] M. Naik, M. R. Nath, A. Wunnava, S. Sahany, and R. Panda, "A new adaptive cuckoo search algorithm," in 2015 IEEE 2nd International Conference on Recent Trends in Information Systems (ReTIS), Jul. 2015, pp. 1–5, doi: 10.1109/ReTIS.2015.7232842.

П

- [41] A. B. Mohamad, A. M. Zain, and N. E. N. Bazin, "Cuckoo search algorithm for optimization problems a literature review and its applications," *Applied Artificial Intelligence*, vol. 28, no. 5, pp. 419–448, May 2014, doi: 10.1080/08839514.2014.904599.

- [42] R. A. de L. Moreto, C. E. Thomaz, and S. P. Gimenez, "Gaussian fitness functions for optimizing analog CMOS integrated circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 36, no. 10, pp. 1620–1632, Oct. 2017, doi: 10.1109/TCAD.2017.2661804.

- [43] K. Garradhi, N. Hassen, and K. Besbes, "Low voltage low power analog circuit design OTA using signal attenuation technique in universal filter application," in 2015 IEEE 12th International Multi-Conference on Systems, Signals & Devices (SSD15), Mar. 2015, pp. 1–7. doi: 10.1109/SSD.2015.7348263.

- [44] R. Pereira-Arroyo, F. Nicaragua-Guzmán, and A. Chacón-Rodríguez, "Design of an operational transconductance amplifier applying multiobjective optimization," in *Proceedings of the Argentine-Uruguay School of Micro-Nanoelectronics, Technology* and Applications 2010, EAMTA 2010, 2010, pp. 12–17.

- [45] R. Laajimi, N. Gueddah, and M. Masmoudi, "A novel design method of two-stage CMOS operational transconductance amplifier used for wireless sensor receiver," *International Journal of Computer Applications*, vol. 39, no. 11, pp. 1–11, Dec. 2012, doi: 10.5120/4861-7093.

- [46] D.-S. Lee, A. Dadashi, and K.-Y. Lee, "A high DC-gain modified CMOS OTA," in 2013 International SoC Design Conference (ISOCC), Nov. 2013, pp. 329–332. doi: 10.1109/ISOCC.2013.6864041.

- [47] D. D. Mirković, P. M. Petković, I. Dimitrijević, and I. Mirčić, "Operational transconductance amplifier in 350nm CMOS technology," *Electronics ETF*, vol. 19, no. 1, pp. 32–37, Jul. 2015, doi: 10.7251/ELS1519032M.

- [48] O. Abdelfattah, G. Roberts, I. Shih, and Y.-C. Shih, "A 0.35-V bulk-driven self-biased OTA with rail-to-rail input range in 65 nm CMOS," in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), May 2015, pp. 257–260. doi: 10.1109/ISCAS.2015.7168619.

- [49] M. Yang and G. W. Roberts, "Synthesis of high gain operational transconductance amplifiers for closed-loop operation using a generalized controller-based compensation method," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 11, pp. 1794–1806, Nov. 2016, doi: 10.1109/TCSI.2016.2599180.

- [50] M. N. Sabry, H. Omran, and M. Dessouky, "Systematic design and optimization of operational transconductance amplifier using gm/ID design methodology," *Microelectronics Journal*, vol. 75, pp. 87–96, May 2018, doi: 10.1016/j.mejo.2018.02.002.

- [51] S. Dong, C. Liu, X. Xin, and X. Tong, "A three-stage OTA with hybrid active miller enhanced compensation technique for large to heavy load applications," *Microelectronics Journal*, vol. 115, pp. 1–10, Sep. 2021, doi: 10.1016/j.mejo.2021.105199.

- [52] Z. M'Harzi, M. Alami, and F. Temcamani, "Novel current-controlled negative resistance based on simplified negative current-controlled conveyors," in 2017 International Conference on Advanced Technologies for Signal and Image Processing (ATSIP), May 2017, pp. 1–6. doi: 10.1109/ATSIP.2017.8075606.

- [53] A. Garbaya, M. Kotti, N. Drira, M. Fakhfakh, E. Tlelo-Cuautle, and P. Siarry, "An RBF-PSO technique for the rapid optimization of (CMOS) analog circuits," in 2018 7th International Conference on Modern Circuits and Systems Technologies (MOCAST), May 2018, pp. 1–4. doi: 10.1109/MOCAST.2018.8376657.

- [54] M. A. Yakout and T. A. Alawadi, "A novel simple BiCMOS Current Controlled Current Conveyor for RF applications," International Journal of Electronics Letters, vol. 8, no. 3, pp. 269–284, Jul. 2020, doi: 10.1080/21681724.2019.1600726.

- [55] A. Lberni, A. Ahaitouf, M. A. Marktani, and A. Ahaitouf, "Sizing of second generation current conveyor using evolutionary algorithms," in 2019 International Conference on Intelligent Systems and Advanced Computing Sciences (ISACS), Dec. 2019, pp. 1–5, doi: 10.1109/ISACS48493.2019.9068896.

- [56] S. Mallick, R. Kar, and D. Mandal, "Optimal design of second generation current conveyor using craziness-based particle swarm optimisation," *International Journal of Bio-Inspired Computation*, vol. 19, no. 2, pp. 87–96, 2022, doi: 10.1504/IJBIC.2022.121234.

## **BIOGRAPHIES OF AUTHORS**

Israa Mohammed Rasheed was born in Babylon, Iraq, in 1995. She is received degree B.Sc. in Department of Electronics and Communications from the University of Babylon (2016) in Iraq and my M.Sc. degrees in Electronics and Communication Engineering from the University of Babylon (2019) in Iraq. Now she is a Ph.D student at University of Babylon. She can be contacted at email: engisraajadui95@gmail.com.

**Prof. Dr. Hassan Jasim Motlak** was born in Baghdad on 1966. He has received B.Sc and M.Sc from University of Technology; Baghdad on 1991 and 2002 resepcively, have received Ph.D. from University of JMI, New Delhi India. The interesting field is design of analog signal processing devices for high frequency applications. He can be contacted at email: hssn\_jasim@yahoo.com.