ISSN: 2302-9285. DOI: 10.11591/eei.v9i3.1784

# Simulations of the CNFETs using different high-k gate dielectrics

# Ankita Dixit, Navneet Gupta

Nanomaterial Device Laboratory, Department of Electrical and Electronics Engineering, Birla Institute of Technology and Science, Pilani, India

#### **Article Info**

# Article history:

Received Sep 10, 2019 Revised Oct 24, 2019 Accepted Dec 31, 2019

#### Keywords:

Carbon nanotube (CNT)

Carbon nanotube field effect

transistor (CNTFET)

Device simulation

Gate-all-around structure

High-k gate dielectrics

#### **ABSTRACT**

In this paper we presented the analysis of carbon nanotube field effect transistors (CNFETs) using various high-k gate dielectric materials. The objective of this work was to choose the best possible material for gate dielectric. This paper also presented the study on the effect of thickness of gate dielectric on the performance of the device. For the analysis (19, 0) CNT was considered because the diameter of (19, 0) CNT is 1.49 nm and the CNFETs have been fabricated with the CNT diameter of ~1.5 nm. It has been observed that La<sub>2</sub>O<sub>3</sub> is the best gate dielectric material followed by HfO<sub>2</sub> and ZrO<sub>2</sub>. It was also observed that as thickness of gate dielectric material reduces, drain current of CNFET increases very marginally. The outcomes of this study matches with the analytical results and hence confirm the results.

This is an open access article under the <u>CC BY-SA</u> license.

943

# Corresponding Author:

Navneet Gupta,

Department of Electrical and Electronics Engineering,

Birla Institute of Technology and Science,

Pilani, Rajasthan, 333031, India. Email: ngupta@pilani.bits-pilani.ac.in

# 1. INTRODUCTION

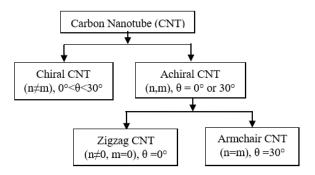

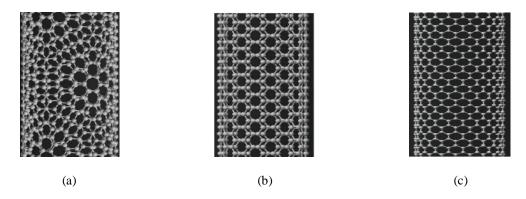

For many years, silicon (Si) has been used as a basic material in the fabrication of transistors, However the problem associated with attempting to scale down traditional semiconductor devices (Si- MOSFET) have led researchers to look into other material devices such as carbon nanotube field effect transistors (CNFETs) as alternative. Carbon nanotubes (CNTs) have been the subject of a lot of scientific research in recent years, not only due to their small size but also because of their remarkable mechanical properties, electronic (high mobility, high transconductions and high current density) properties [1] and many potential applications [2, 3]. As shown in Figure 1, based on the chirality, CNTs can be classified into two types: chiral CNT and achiral CNT. Achiral CNT is further divided into Zigzag CNT and Armchair CNT. Figure 2 shows the schematic view of these CNTs. The diameter (d) and energy band gap (Eg) of CNT is calculated by following (1-2) [4]:

$$d = 0.078 \times \sqrt{n^2 + m^2 + nm} \tag{1}$$

$$E_g = \frac{2a_{cc}t}{d} \approx \frac{0.8}{d} \tag{2}$$

Journal homepage: http://beei.org

944 🗖 ISSN: 2302-9285

where (n, m) are chirality of CNT,  $a_{c-c}$  is nearest neighbor C-C bonding distance (~0.142 nm) and t is the tight binding energy (~3 eV). The diameter of the SWCNT ranges from 0.5 nm to 5 nm [5].

Figure 1. Classification of carbon nanotubes

Figure 2. Schematic view of carbon nanotube, (a) Chiral (12, 9) (b) Armchair (9, 9) and (c) Zigzag (19, 0)

CNFETs are being studied for a wide variety of applications, including logic devices, memory devices, sensors etc. However, to predict the ultimate performances of these novel nano devices and to further offer guidance and cost reduction of the technological development, accurate and reliable simulation tools appear as key issues. The performance of CNFET depends on gate dielectric, source and drain materials. It is well established fact that reduction in device dimension leads to increase in leakage current. One way to reduce the possibility of leakage current is to use high-k dielectric materials as gate. Commonly reported high-k dielectrics include Hafnium oxide (HfO2), Alumina (Al2O3), Hafnium Silicate (HfSiO4), Zirconia (ZrO<sub>2</sub>), Yttrium Oxide (Y<sub>2</sub>O<sub>3</sub>), Lanthanum oxide (La<sub>2</sub>O<sub>3</sub>), Silicon dioxide (SiO<sub>2</sub>) and Silicon Nitride  $(Si_3N_4)$  [6-15]. Now the issue is that the material properties including relative dielectric constant ( $\varepsilon_r$ ), energy band gap (E<sub>0</sub>), conduction band offset (CBO) and coefficient of thermal expansion (CTE) affects the choice of dielectric material to be used. The analysis for the selection of the best gate dielectric materials can be done analytically and also by simulation. In our recent work [16, 17], it was found analytically that La<sub>2</sub>O<sub>3</sub> and HfO2 are the best gate dielectrics for CNFET. Analytical study was done using three material selection methodologies; Ashby's Approach, TOPSIS method and VIKOR analysis [18]. According to Ashby's approach, the best gate dielectric is La<sub>2</sub>O<sub>3</sub>. Table 1 shows the ranking of gate dielectrics obtained using TOPSIS and VIKOR analytical approaches. However, before going for fabrication of device it is important to develop the device in virtual environment. Therefore, simulation study helps in comparing the simulated results with analytical work reported earlier.

The performance of CNFET depends on the geometry of device (*i.e.* planar or gate-all-around structure) and the thickness of gate dielectric. Fabricated results for the planar structure [19-23] and gate-all-around (GAA) structure [24, 25] show that the performance of CNFET is affected by the various thickness of gate dielectric material [26, 27]. In planar structure, the performance of device is affected by fringing effect while the GAA structure is expected to be ideal geometry that maximizes the electrostatic gate control in FETs [28, 29]. The paper is organized as follows: Section 2 describes the design of CNFET

and input parameters. Section 3 provides the simulation results for the selection of the best gate dielectric with the suitable thickness of dielectric and observations. The concluding remarks are given in Section 4.

| Table 1. | Ranking | of gate | dielectrics | using anal | vtical | approach | [16] |

|----------|---------|---------|-------------|------------|--------|----------|------|

|          |         |         |             |            |        |          |      |

| Dielectric materials - | Ranking based on analytical approaches |       |  |  |

|------------------------|----------------------------------------|-------|--|--|

| Dielectric materials - | TOPSIS                                 | VIKOR |  |  |

| $SiO_2$                | 7                                      | 7     |  |  |

| $Al_2O_3$              | 5                                      | 3     |  |  |

| $HfSiO_4$              | 6                                      | 6     |  |  |

| $\mathrm{ZrO}_2$       | 3                                      | 4     |  |  |

| $La_2O_3$              | 1                                      | 1     |  |  |

| $Y_2O_3$               | 4                                      | 5     |  |  |

| $HfO_2$                | 2                                      | 2     |  |  |

| $Si_3N_4$              | 8                                      | 8     |  |  |

# 2. DEVICE STRUCTURE AND SIMULATION

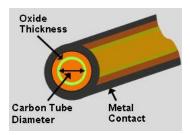

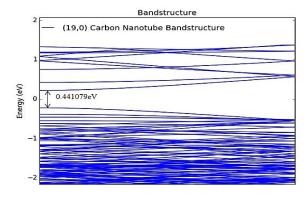

In this work, we have simulated the cylindrical CNFET with different gate dielectric materials as shown in Table 2 and also studied the effect of thickness of dielectric layer (i.e. 3nm, 5nm, 7nm, 8nm, 10nm and 20nm) on the drain current ( $I_d$ ). The schematic view of CNFET is shown in Figure 3. The electronic transport mechanism in the CNFET is ballistic. The diameter and energy band gap have been simulated by using QuantumWise Atomistic Tool Kit (ATK) software. The diameter and energy band gap of (19, 0) CNT comes out to be 1.490nm and 0.441079eV, as shown in Figures 4 and 5. Table 3 shows the input parameters of CNFET for the simulation.

Table 2. Relative dielectric permittivity of various high-k dielectric materials

| S. No. | Dielectric materials | Relative dielectric constant $(\varepsilon_r)$ |

|--------|----------------------|------------------------------------------------|

| 1      | SiO <sub>2</sub>     | 3.9                                            |

| 2      | $Al_2O_3$            | 9                                              |

| 3      | $HfSiO_4$            | 11                                             |

| 4      | $ZrO_2$              | 25                                             |

| 5      | $La_2O_3$            | 30                                             |

| 6      | $Y_2O_3$             | 15                                             |

| 7      | $HfO_2$              | 25                                             |

| 8      | $Si_3N_4$            | 7                                              |

Figure 3. Schematic view of carbon nanotube field effect transistor using nano-hub [30]

Figure 4. Diameter of (19, 0) CNT

Figure 5. Energy bandstructure for (19, 0) CNT

946 🗖 ISSN: 2302-9285

| Two to the purchase for the simulation of end 21 |                             |                               |          |  |

|--------------------------------------------------|-----------------------------|-------------------------------|----------|--|

| Input Parameters                                 | Values                      | Input Parameters              | Values   |  |

| Gate dielectric thickness                        | 3 nm                        | Final drain voltage           | 1 eV     |  |

| Insulator dielectric material                    | $La_2O_3(\varepsilon_r=30)$ | Number of bias points (drain) | 11       |  |

| temperature                                      | 300 K                       | Threshold voltage             | 0.32     |  |

| Final gate value                                 | 0 eV                        | Gate control parameter        | 0.88     |  |

| Number of bias points (gate)                     | 0.3eV                       | Drain control parameter       | 0.035    |  |

| Initial drain voltage                            | 3V                          | Series resistance             | 0 (ohms) |  |

|                                                  |                             | NT Diameter                   | 1.49 nm  |  |

# 3. RESULTS AND DISCUSSION

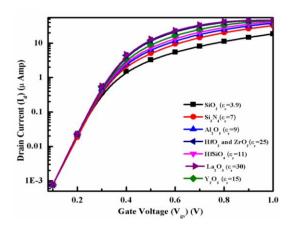

In order to get the best gate dielectric material for CNFET, transfer characteristics and output characteristics have been analyzed for different gate dielectric materials. Figure 6 shows the transfer characteristics of CNFET for different high-k gate dielectric materials. In this plot SiO<sub>2</sub> is also considered for the comparison purpose. The value of drain to source voltage ( $V_{ds}$ ) is assumed as 0.3V. It has been observed from the plot that corresponding to each gate voltage ( $V_{gs}$ ), La<sub>2</sub>O<sub>3</sub> gives the highest value of drain current, followed by HfO<sub>2</sub> and ZrO<sub>2</sub>. However, at low values of gate voltage this difference is negligible. The subthreshold swing and current on/off ratio for La<sub>2</sub>O<sub>3</sub> are 65.41mV/dec and 1.8089x 10<sup>6</sup>, respectively. The high current on/off ratio shows the figure of merit for having low leakage power and high performance for CNFET.

Figure 7 shows the output characteristics of CNFET for different high-k gate dielectrics materials. In this plot, the value of gate to source voltage ( $V_{gs}$ ) is assumed as 0.3V. It has been observed from the plot that corresponding to each drain voltage ( $V_{ds}$ ), drain current ( $I_d$ ) increases with increase in relative dielectric constant ( $\epsilon_r$ ). It has been shown that La<sub>2</sub>O<sub>3</sub> ( $\epsilon_r$ =30) has the highest output drain current ( $I_d$ =1.19  $\mu$  Amp) followed by HfO<sub>2</sub> and ZrO<sub>2</sub> among all the possible gate dielectric materials.

SiO<sub>2</sub> (c;=3.9)

Si<sub>3</sub> N<sub>2</sub> (c;=7)

A<sub>3</sub>O<sub>3</sub> (c;=9)

HIGO<sub>2</sub> and ZrO<sub>3</sub> (c;=25)

HISiO<sub>4</sub> (c;=11)

La<sub>2</sub>O<sub>3</sub> (c;=30)

Y<sub>2</sub>O<sub>3</sub> (c;=15)

0 0.0 0.2 0.4 0.6 0.8 1.0

Drain Voltage (V<sub>d.</sub>) (V)

Figure 6. Transfer characteristics of CNFET with different gate dielectric

Figure 7. Output characteristics of CNFET with different gate dielectric

Table 4 shows the output drain current ( $I_d$ ) for different gate dielectric materials. In CNFET, the analysis of transfer characteristics and output characteristics with different high-k gate dielectric materials show that  $La_2O_3$  is the best gate dielectric material among all possible gate dielectrics which is followed by  $HfO_2$  and  $ZrO_2$ . The effect of thickness of gate dielectric layer in CNFET also studied with the best gate dielectric materials *i.e.*  $La_2O_3$  and  $HfO_2$ . Table 5 contains the output results of the simulated device which has both  $La_2O_3$  and  $HfO_2$  results with the variation of the thickness of dielectric layer.

Table 4. Drain current in CNFET with the possible gate dielectrics

| S.No. | Dielectric Materials | Drain Current $(I_d)(\mu Amp.)$ |

|-------|----------------------|---------------------------------|

| 1     | $SiO_2$              | 0.605                           |

| 2     | $Al_2O_3$            | 0.865                           |

| 3     | $HfSiO_4$            | 0.927                           |

| 4     | $ZrO_2$              | 1.15                            |

| 5     | $La_2O_3$            | 1.19                            |

| 6     | $Y_2O_3$             | 1.02                            |

| 7     | $HfO_2$              | 1.15                            |

| 8     | $Si_3N_4$            | 0.785                           |

Table 5. Output drain current for CNFET with the two best dielectrics (*i.e.* La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>) by various thickness of gate dielectrics

| thickness of gate dielectries |      |                  |                       |  |

|-------------------------------|------|------------------|-----------------------|--|

| S.No.                         | Tox  | $I_d$ (µAmp) for | I <sub>d</sub> (μAmp) |  |

| 5.110.                        |      | $La_2O_3$        | for HfO <sub>2</sub>  |  |

| 1                             | 3nm  | 1.27             | 1.24                  |  |

| 2                             | 5nm  | 1.23             | 1.19                  |  |

| 3                             | 7nm  | 1.2              | 1.16                  |  |

| 4                             | 8nm  | 1.19             | 1.15                  |  |

| 5                             | 10nm | 1.17             | 1.13                  |  |

| 6                             | 20nm | 1.12             | 1.08                  |  |

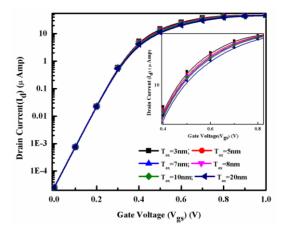

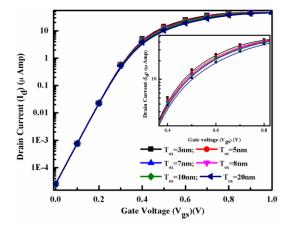

The variation of  $I_d$  with respect to  $V_{gs}$  for various gate dielectric thickness ( $T_{ox}$ ) (i.e. 3nm, 5nm, 7nm, 8nm, 10nm, 20nm) with gate dielectric material  $La_2O_3$  and  $HfO_2$  is shown in Figure 8 and Figure 9, respectively. It has been observed from the plots that the current on/off ratio increases with decreases the thickness of gate dielectric material. It has been shown that the highest on current ( $I_{on}$ ) of CNFET with  $La_2O_3$  and  $HfO_2$  are  $46.54\mu$  Amp and 46.52  $\mu$  Amp for the thickness of gate dielectric material of 3nm.

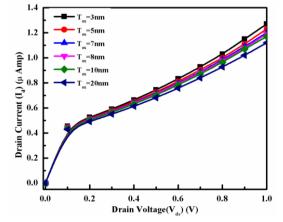

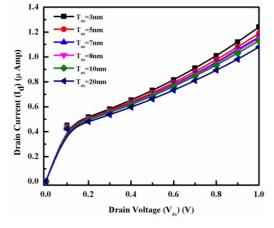

The variation of  $I_d$  with respect to  $V_{ds}$  for various gate dielectric thickness with gate dielectric material  $La_2O_3$  and  $HfO_2$  at  $V_{gs}$  of 0.3V is shown in Figure 10 and Figure 11, respectively. It has been observed from the plot that the drain current of CNFET increases very marginaly with decreases the thickness of gate dielectric layer. This shows that the resistivity of CNFET is proportional to the thickness of gate dielectric material. It has been shown that  $I_d$  is the highest for the thickness of gate dielectric material of 3nm.

Figure 8. Transfer characteristics of CNFET with  $La_2O_3$  for various dielectric thickness

Figure 9. Transfer characteristics of CNFET with HfO<sub>2</sub> for various dielectric thickness

Figure 10. Output characteristics of CNFET with La<sub>2</sub>O<sub>3</sub> for various dielectric thickness

Figure 11. Output characteristics of CNFET with HfO<sub>2</sub> for various dielectric thickness

#### 4. CONCLUSION

CNFET with various high-k gate dielectrics has been investigated. The analysis was done using simulations and results show that La<sub>2</sub>O<sub>3</sub> shows the best result followed by HfO<sub>2</sub> as compared to other possible materials. Therefore, it is expected that using La<sub>2</sub>O<sub>3</sub> as gate material into CNFET may be useful for producing high performance FETs. For the thickness of gate dielectric, the results show that as the thickness of dielectric decrease from 20 nm to 3 nm, output current and current on/off ratio increase which shows the low leakage current and better gate control in CNFET.

#### **ACKNOWLEDGEMENTS**

Authors acknowledge the financial support of Defence Research and Development Organisation (DRDO) [ERIP/ER/DGMED&OS/990416502/M/01/1657] for carrying out research work reported this paper.

#### REFERENCES

- [1] F. J. Niven et al., "Influence of Annealing on Thermal and Electrical Properties of Carbon Nanotube Yarns," *Carbon*, vol. 99, pp. 484-490, 2016.

- [2] K. Safari, A. Rafiee and H-D Oskouei, "Organic Semiconductor and Transistor Electrical Characteristic Based on Carbon Nanotubes," *Bulletin of Electrical Engineering and Informatics*, vol. 5, no. 1, pp. 79-87, 2016.

- [3] H. Ghabri, D. B. Issa and H. Samet, "New Optimized Reconfigurable ALU Design Based on DG-CNTFET Nanotechnology," *International Journal of Reconfigurable and Embedded Systems*, vol. 7, no. 3, pp.189-196, 2018.

- [4] M. S Lundstrom and J. Guo, "Nanoscale Transistors: Device Physics, Modeling and Simulation. Nanoscale Transistors: Device Physics, Modeling and Simulation," *Springer*, pp. 159-168, 2006.

- [5] H-S. P. Wong and D. Akinwande, "Carbon Nanotube and Graphene Device Physics," Cambridge University Press, New York, 2011.

- [6] M. Shafizadeh and A. Rezai, "Improved device performance in a CNTFET using La<sub>2</sub>O<sub>3</sub> high-k dielectrics," J. Comput. Electron., vol. 16, no. 2, pp. 221–227, 2017.

- [7] K. Kandpal and N. Gupta, "Investigations on high-K dielectrics for low threshold voltage and low leakage zinc oxide thin-film transistor, using material selection methodologies," *J. Mater. Sci: Mater. Electro.*, vol. 27, no. 6, pp. 5972-5981, 2016.

- [8] J. Robertson and B. Falabretti, "Band offsets of high K gate oxides on III-V semiconductors," J. Appl. Phys., vol. 100, no. 1, pp. 014111-8, 2006.

- [9] A. Shaukat, R. Umer and N. Islam, "Impact of dielectric material and oxide thickness on the performance of Carbon Nanotube Field Effect Transistor," *IEEE International Conference on Nanotechnology*, pp. 250-254, 2017.

- [10] J. C. Dutta and H. R. Thakur, "Sensitivity Determination of CNT-Based ISFETs for Different High-Dielectric Materials," *IEEE Sensors Letters*, vol. 1, no. 2, pp. 1-4, 2017.

- [11] N. Yu, et al., "3D Assembly of Carbon Nanotubes for Field-effect Transistor Fabrication through Nanomanipulation and Electron-beam-induced Deposition," J. Micromech. Microeng., vol. 27, no. 10, 2017.

- [12] P. B. Agarwal, A. K. Singh and A. Agarwal, "Stable metal-CNT contacts using shadow mask technique for CNTFET fabrication," *AIP Conference Proceedings*, pp. 030002 (1-4), 2018.

- [13] E.-K. Jeon, et al., "Electromechanical properties of single-walled carbon nanotube devices on micromachined cantilevers," *J. Micromech. Microeng.*, vol. 22, no. 11, 2012.

- [14] M. Ossaimee, S. Gamal and A. Shaker, "Gate dielectric constant engineering for suppression of ambipolar conduction in CNTFETs," *Electronics Letters*, vol. 51, no. 6, pp. 503-504, 2015.

- [15] R. Djamil, et al., "Impacts of high-k gate dielectrics and low temperature on the performance of nanoscale CNTFETs," *J. Comput. Electro.*, vol. 15, no. 4, pp. 1308-1315, 2016.

- [16] A. Dixit, and N. Gupta, "Investigation into gate dielectric material using different optimization techniques in carbon nanotube field effect transistors Investigation into gate dielectric material using different optimization techniques in carbon nanotube field effect transistors," *Journal of Micromechanics and Microengineering*, vol. 29, pp. 1-6, 2019.

- [17] A. Dixit and N. Gupta, "Analysis of Different Gate Dielectric Materials in Carbon Nanotube Field Effect Transistor (CNFET) using Optimization Technique," *IEEE Electron Device Kolkata Conference (EDKCON)*, pp. 354-357, 2018.

- [18] V. Garg and N. Gupta, "Selection of Gate Dielectrics for ZnO Based Thin-Film Transistors," *Bulletin of Electrical Engineering and Informatics*, vol. 5, no. 2, pp. 213-218, 2016.

- [19] J. Kimbrough, et al., "Deposition and Alignment of Carbon Nanotubes with Dielectrophoresis for Fabrication of Carbon Nanotube Field-Effect Transistors," 2018 *IEEE International Conference on Manipulation, Manufacturing and Measurement on the Nanoscale (3M-NANO)*, Hangzhou, pp. 308-311, 2018.

- [20] T. Srimani, et al., "Negative Capacitance Carbon Nanotube FETs," *IEEE Electron Device Letters*, vol. 39, no. 2, pp. 304-307, 2018.

- [21] K. C. Narasimhamurthy and R. Paily, "Fabrication of Carbon Nanotube Field Effect Transistor," *IETE Technical Review*, vol. 28, no. 1, pp. 57-69, 2014.

П

- [22] A. Javey, et al., "Self-Aligned Ballistic Molecular Transistors and Electrically Parallel Nanotube Arrays," *Nano Lett.*, vol. 4, no. 7, pp. 1319-1322, 2004.

- [23] A. Javey, et al., "Carbon Nanotube Field-Effect Transistors with Integrated Ohmic Contacts and High-κ Gate Dielectrics," *Nano lett.*, vol. 4, no. 3, pp.447-450, 2004.

- [24] Chez, Z., et al., "Externally Assembled Gate-All-Around CarbonNanotube Field-Effect Transistor," IEEE Elec. Dev. Lett., vol. 29, no. 2, pp. 183-185, 2008.

- [25] A. D. Franklin, et al., "Scalable and Fully Self-Aligned n-Type Carbon Nanotube Transistors with Gate-All-Around," 2012 International Electron Devices Meeting, 2012.

- [26] A. D. Franklin, et al., "Carbon Nanotube Complementary Wrap-Gate Transistors," Nano Lett., vol. 13, no. 6, pp. 2490-2495, 2013.

- [27] A. D. Franklin, et al., "Sub-10 nm Carbon Nanotube Transistor," Nano Lett., vol. 12, no. 2, pp. 758-762, 2012.

- [28] B. Jena, et al., "Performance analysis of undoped cylindrical gate all around (GAA) MOSFET at subthreshold regime," Adv. Nat. Sci. Nanosci. Nanotechnology, vol. 6, no. 3, pp. 035010-4, 2015.

- [29] S. Chaudhury and S. K. Sinha, "Carbon Nanotube and Nanowires for Future Semiconductor Devices Applications," Nanoelectronics, pp. 375–398, 2019.

- [30] A. Rahman, et al., "FETToy," 2006. [Online]. Available: 10254/nanohub-r220.4.

#### **BIOGRAPHIES OF AUTHORS**

Ankita Dixit is currently pursuing the Ph.D. degree in the field of micro/nano electronics from Birla Institute of Technlogy and Science (BITS), Pilani, Rajasthan, India. She received B.Tech. degree with honours in electronics and communication engineering from Rajasthan Technical university, Kota, Rajasthan, India in 2013. She completed her M.Tech in Nanotechnology from University of Rajasthan, Jaipur, in 2017. She has worked as an intern at metallurgical department in Malaviya National Institute of Technology, Jaipur.

**Prof. Navneet Gupta** is currently Associate Professor in Department of Electrical and Electronics Engineering at BITS-Pilani, Rajasthan, India. He received M.Sc Physics with specialization in Advanced Electronics from H. N. B Garhwal University (a Central University) (HNBGU), Srinagar in 1995 with first rank in the University and was awarded Gold Medal. He received M.Tech in Materials Technology in 1998 from Indian Institute of Technology (IIT-BHU)-Varanasi (formerly IT-BHU). He completed his Ph.D in the field of Semiconductor Devices Modelling from HNBGU in 2005. His current research interests are in the areas of Semiconductor Device modeling, Computational Material Science, Electromagnetics and Antenna design. He has published 108 research papers in international and national journals and conferences. He is Fellow of The Institution of Engineers (India), Senior member of IEEE and life members of other professional bodies. He is expert reviewer of many reputed International Journals including IEEE, Springer, Elsevier and IE (I).